AMD Geode™ LX Processors Data Book 471

Video Input Port

33234H

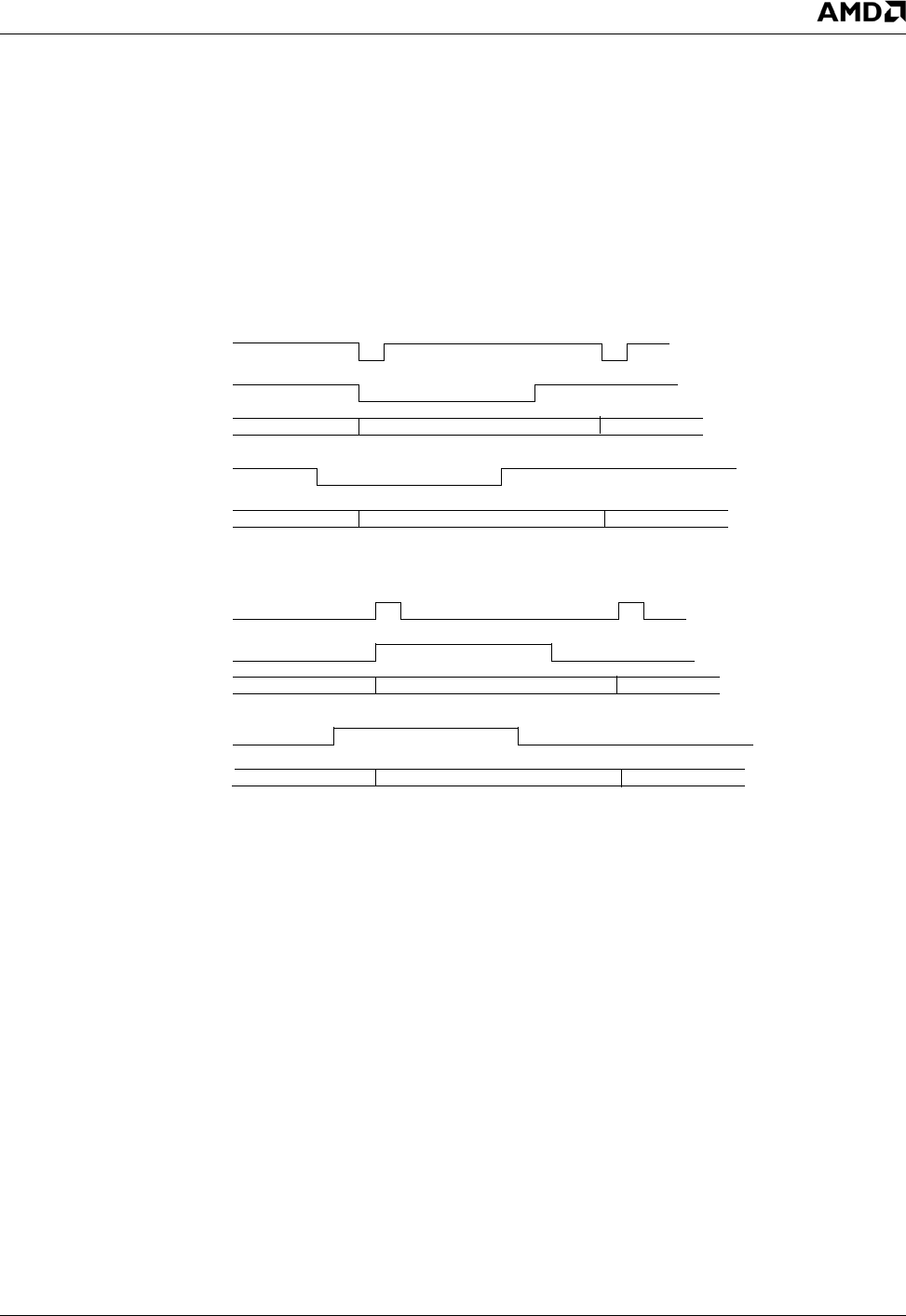

6.9.8 BT.601 Mode

BT.601 mode allows reception of 8- or 16-bit video input

which consists of HSYNC, VSYNC, and 8/16 bit data. Verti-

cal and horizontal start/stop registers provide the informa-

tion for data capture in each field/frame. The BT.656 SAV/

EAV codes (if present) are ignored. Frame/line timing is

derived from the HSYNC and VSYNC inputs only. Odd/

even field is determined by the leading edges of VSYNC

and HSYNC. Default field detection is shown in Figure 6-

45. A detection window is programmable using the VIP

Memory Offset 50h. If the leading edge of VSYNC occurs

within the window, the field is odd. If the leading edge of

VSYNC occurs outside the window, the field is even. The

VIP Memory Offset 50h default value requires that the

HSYNC and VSYNC leading edges occur simultaneously

for odd field detection (see Figure 6-46 on page 472). The

horizontal and vertical input timings of the input video

frame are also programmable. See Figure 6-47 and Figure

6-48.

Figure 6-45. BT.601 Mode Default Field Detection

HSYNC

VSYNC

ACTIVE LOW HSYNC/VSYNC (HSYNC polarity = 0 / VSYNC polarity = 0)

ACTIVE HIGH HSYNC/VSYNC (HSYNC polarity = 1 / VSYNC polarity = 1)

VSYNC

HSYNC

(for odd field)

(for even field)

even field

odd field

line #1

line #1

even field

odd field (line #1)

(line #1)

even field (line #2)

odd field (line #2)

VSYNC

VSYNC

(for odd field)

(for even field)

even field

odd field

even field

odd field (line #1)

(line #1)

even field (line #2)

odd field (line #2)

Odd field is indicated when leading edge of VSYNC and the leading edge of HSYNC occur simultaneously

(VIP allows for a programmable detection window for odd field).

Even field is indicated when leading edge of VSYNC occurs prior to the leading edge of HSYNC.