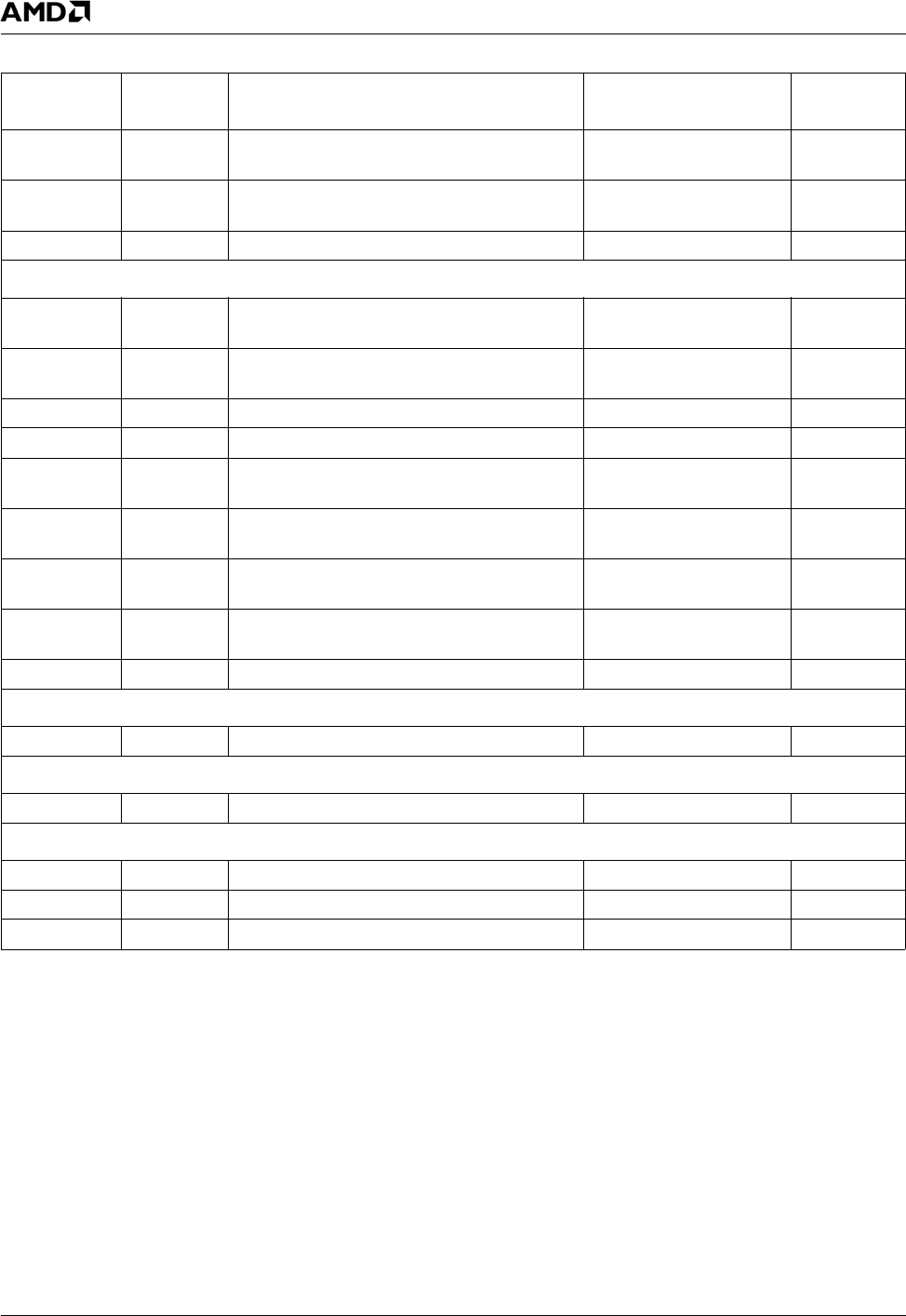

540 AMD Geode™ LX Processors Data Book

GeodeLink™ Control Processor Register Descriptions

33234H

4C000015h R/W GLCP Dot Clock PLL Control

(GLCP_DOTPLL)

000000D7_02000000h Page 557

4C000016h R/W GLCP Debug Clock Control

(GLCP_DBGCLKCTL)

00000000_00000002h Page 559

4C000017h RO Chip Revision ID (GLCP_CHIP_REVID) 00000000_000000xxh Page 559

GLCP I/O Address MSRs

4C000018h R/W - I/O

Offset 00h

GLCP Control (GLCP_CNT) 00000000_000000Fh Page 560

4C000019h R/W - I/O

Offset 04h

GLCP Level 2 (GLCP_LVL2) 00000000_00000000h Page 560

4C00001Ah -- Reserved -- --

4C00001Bh -- Reserved -- --

4C00001Ch R/W - I/O

Offset 10h

GLCP Throttle or C2 Start Delay

(GLCP_TH_SD)

00000000_00000000h Page 561

4C00001Dh R/W - I/O

Offset 14h

GLCP Scale Factor (GLCP_TH_SF) 00000000_00000000h Page 561

4C00001Eh R/W - I/O

Offset 18h

GLCP Processor Throttle Off Delay

(GLCP_TH_OD)

00000000_00000000h Page 562

4C00001Eh R/W - I/O

Offset 18h

GLCP Processor Throttle Off Delay

(GLCP_TH_OD)

00000000_00000000h Page 562

4C00001Fh -- Reserved -- --

GLCP Debug Interface MSRs

4C000023h R/W GLCP DAC (GLCP_DAC) 00000000_00000000h Page 563

GLCP IGNNE I/Os

F0h, F1h W GLCP IGNNE I/Os NA Page 562

GLCP I/O Companion Interface MSRs

4C000031h R/W CPU A20M Signal (MSR_A20M) 00000000_00000000h Page 564

4C000033h R/W CPU INIT Signal (MSR_INIT) 00000000_00000000h Page 564

4C000036h RO GLIU Device Interrupt Status (MSR_INTAX) 00000000_00000000h Page 565

Table 6-86. GLCP Specific MSRs Summary (Continued)

MSR

Address Type Register Name Reset Value Reference