AMD Geode™ LX Processors Data Book 621

Instruction Set

33234H

8.1.2 Opcode

The opcode field specifies the operation to be performed by the instruction. The opcode field is either one or two bytes in

length and may be further defined by additional bits in the mod r/m byte. Some operations have more than one opcode,

each specifying a different form of the operation. Certain opcodes name instruction groups. For example, opcode 80h

names a group of operations that have an immediate operand and a register or memory operand. The reg field may appear

in the second opcode byte or in the mod r/m byte.

The opcode may contain w, d, s, and eee opcode fields, for example, as shown in Table 8-26 on page 634.

8.1.2.1 w Field (Operand Size)

When used, the 1-bit w field selects the operand size during 16-bit and 32-bit data operations. See Table 8-4.

8.1.2.2 d Field (Operand Direction)

When used, the 1-bit d field determines which operand is taken as the source operand and which operand is taken as the

destination. See Table 8-5.

8.1.2.3 s Field (Immediate Data Field Size)

When used, the 1-bit s field determines the size of the immediate data field. If the s bit is set, the immediate field of the

opcode is 8 bits wide and is sign-extended to match the operand size of the opcode. See Table 8-6.

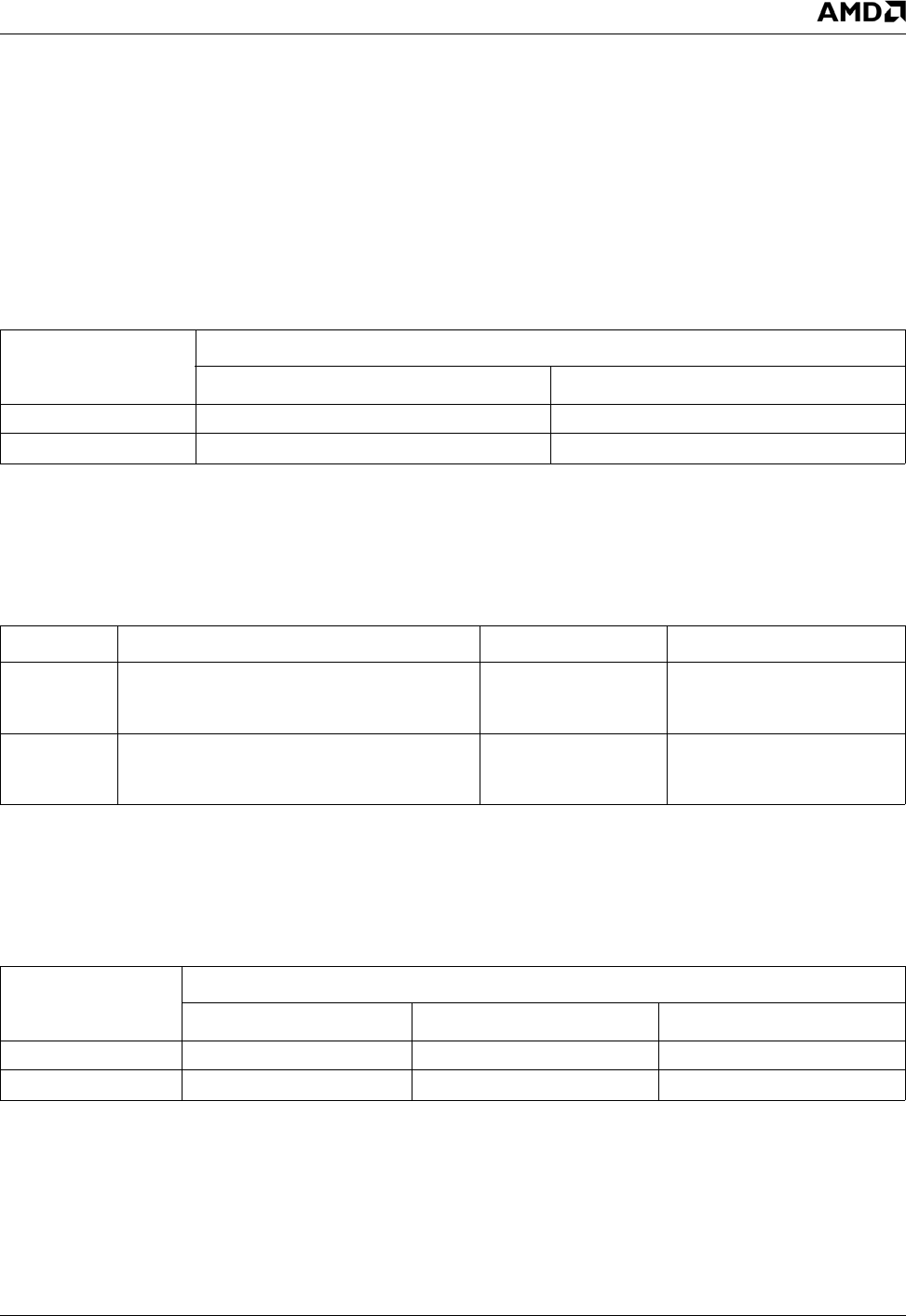

Table 8-4. w Field Encoding

w Field

Operand Size

16-Bit Data Operations 32-Bit Data Operations

0 8 bits 8 bits

1 16 bits 32 bits

Table 8-5. d Field Encoding

d Field Direction of Operation Source Operand Destination Operand

0 Register-to-Register

or

Register-to-Memory

reg mod r/m

or

mod ss-index-base

1 Register-to-Register

or

Memory-to-Register

mod r/m

or

mod ss-index-base

reg

Table 8-6. s Field Encoding

s Field

Immediate Field Size

8-Bit Operand Size 16-Bit Operand Size 32-Bit Operand Size

0 (or not present) 8 bits 16 bits 32 bits

1 8 bits 8 bits (sign-extended) 8 bits (sign-extended)