508 AMD Geode™ LX Processors Data Book

Video Input Port Register Descriptions

33234H

6.10.2.29 VIP VSYNC Error Count (VIP_SYNC_ERR_COUNT)

6.10.2.30 VIP Task A U Even Offset (VIP_TASK_A_U_EVEN_OFFSET)

VIP Memory Offset 78h

Typ e R /W

Reset Value 00000000h

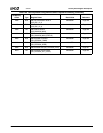

VIP_SYNC_ERR_COUNT Register Map

313029282726252423222120191817161514131211109876543210

VERTICAL_WINDOW VERTICAL_COUNT

VIP_SYNC_ERR_COUNT Bit Descriptions

Bit Name Description

31:24 VERTICAL_

WINDOW

Vertical Window. This field defines the number of VIP clocks the input VBLANK can

vary before it is considered invalid. (16-4095 clocks)

23:0 VERTICAL_

COUNT

Vertical Count. This field provides the check point for verifying that the input data stream

is maintaining consistent VSYNC timing. This count is the minimum number of VIP clocks

expected in an input field (interlaced video) or frame (non-interlaced video). If the number

of video clocks between rising edges of VBLANK is less then this number (or greater

then VERTICAL_COUNT + VERTICAL_WINDOW), a VSYNC error interrupt is gener-

ated and the video_ok output signal is forced low indicating invalid input video. (0-

16,777,215 clocks)

Note: A 60 Hz VBLANK rate @75 MHz input clock = 1,250,000 clocks.

VIP Memory Offset 7Ch

Typ e R /W

Reset Value 00000000h

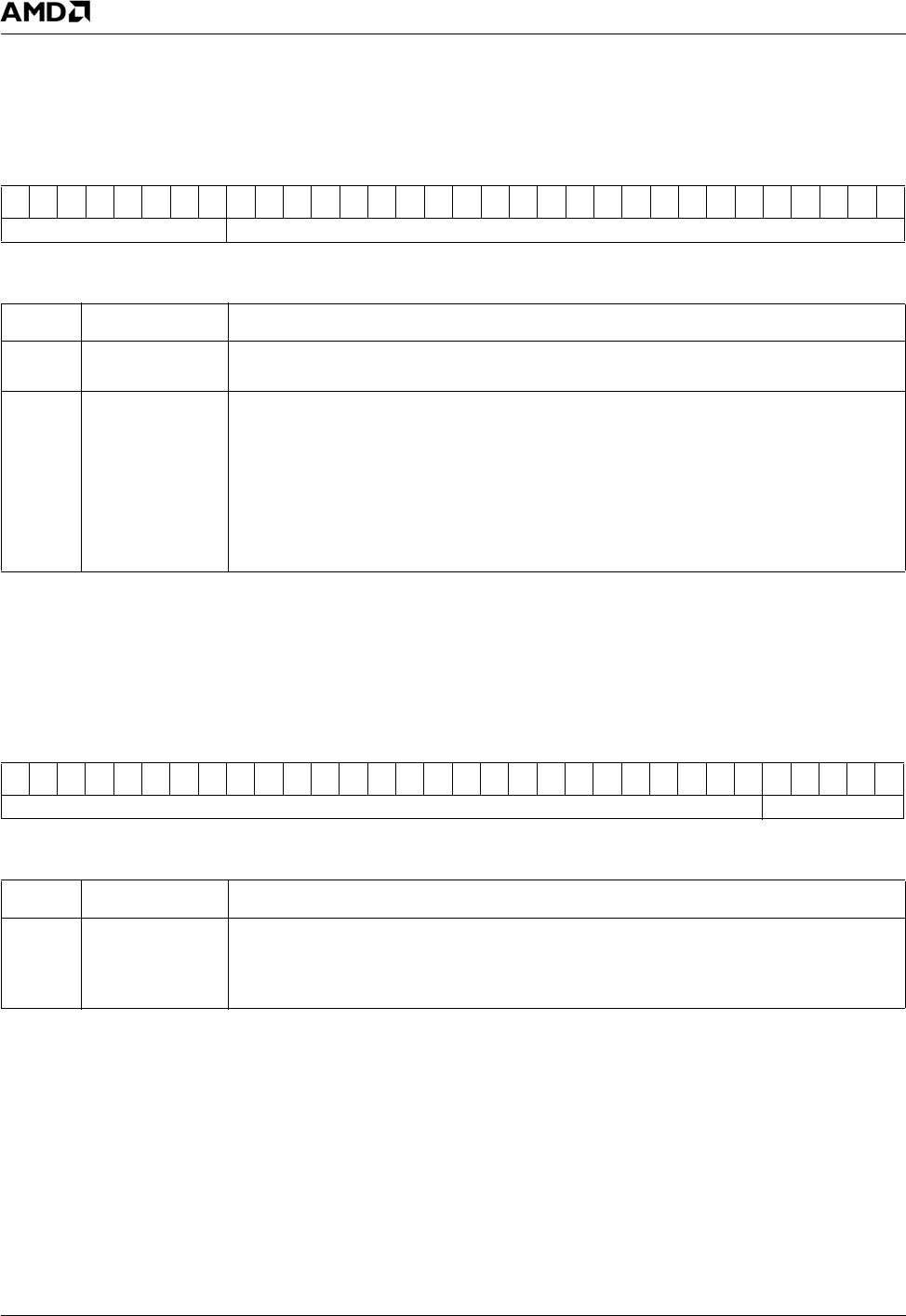

VIP_TASK_A_U_EVEN_OFFSET Register Map

313029282726252423222120191817161514131211109876543210

TASK_A_U_EVEN_OFFSET Program to 00000

VIP_TASK_A_U_EVEN_OFFSET Bit Descriptions

Bit Name Description

31:0 TASK_A_U_

EVEN_OFFSET

Task A U Even Offset. This register determines the starting address of the U buffer for

the even field when in interlaced input mode and data is stored in planar format. This reg-

ister is not used when in non-interlaced input mode. The value in this register needs to be

32-byte aligned. (Bits [4:0] are required to be 00000.)