AMD Geode™ LX Processors Data Book 47

GeodeLink™ Interface Unit

33234H

4.1.2 Port Addressing Exceptions

There are some exceptions to the port addressing rules.

If a module accesses an MSR from within its closest GLIU

(e.g., CPU Core accessing a GLIU0 MSR), then, by con-

vention, the port address should be 0.0.0.0.0.0. But this

port address accesses an MSR within the source module

and not the GLIU as desired. To get around this, if the port

address contains a 0 in the first channel field and then con-

tains a 1 in any of the other channel fields, the access goes

to the GLIU nearest the module sourcing the cycle. By con-

vention, set the MSB of the second channel field,

0.4.0.0.0.0. If the MSR access is to a GLIU farther removed

from the module sourcing the cycle, then there is no con-

vention conflict, so no exception is required for that situa-

tion.

If a module attempts to access an MSR to the channel that

it is connected to, a GLIU error results. This is called a

reflective address attempt. An example of this case is the

CPU Core accessing 3.0.0.0.0.0. Since the CPU Core is

connected to Channel 3 of GLIU0, the access causes a

reflective address error. This exception is continued to the

next GLIU in the chain. The CPU Core accessing

2.1.0.0.0.0 also causes a reflective address error.

To access modules in the AMD Geode companion device,

the port address must go through the GLPCI (PCI control-

ler) in the processor and through the GLPCI in the compan-

ion device. The port address of the MSRs in the

processor’s GLPCI when accessed from the CPU Core is

2.4.0.0.0.0. To get the port address to go through the

GLPCI, the third field needs a non-zero value. By conven-

tion, this is a 2. We now have a port address of 2.4.2.0.0.0.

But this accesses the MSRs in the GLPCI in the compan-

ion device. The port to be accessed must be added in the

fourth field, 2.4.2.5.0.0, to access the AC97 audio bus mas-

ter, for example.

To access the GLIU in the companion device, the same

addressing exception occurs as with GLIU0 due to the

GLPCI’s address. A port address of 2.4.2.0.0.0 accesses

the companion device’s GLPCI, not the GLIU. To solve this,

a non-zero value must be in at least one of the two right-

most port fields. By convention, a 4 in the left-most port

field is used. To access the companion device’s GLIU from

the CPU Core, the port address is 2.4.2.0.0.4.

Table 4-2 shows the MSR port address to access all the

modules in a AMD Geode LX processor/CS5536 system

with the CPU Core as the source module. Included in the

table is the MSR port address for module access using the

GLCP and GLPCI as the source module. However, under

normal operating conditions, accessing MSRs is from the

CPU Core. Therefore, all MSR addresses in the following

chapters of this data book are documented using the CPU

Core as the source.

4.1.3 Memory and I/O Mapping

The GLIU decodes the destination ID of memory requests

using a series of physical to device (P2D) descriptors.

There can be up to 32 descriptors in each GLIU. The GLIU

decodes the destination ID of I/O requests using a series of

I/O descriptors (IOD).

4.1.3.1 Memory Routing and Translation

Memory addresses are routed and optionally translated

from physical space to device space. Physical space is the

32-bit memory address space that is shared between all

GeodeLink devices. Device space is the unique address

space within a given device. For example, a memory con-

troller may implement a 4 MB frame buffer region in the 12-

16 MB range of main memory. However, the 4 MB region

may exist in the 4 GB region of physical space. The actual

location of the frame buffer in the memory controller with

respect to itself is a device address, while the address that

all the devices see in the region of memory is in physical

space.

Memory request routing and translation is performed with a

choice of five descriptor types. Each GLIU may have any

number of each descriptor type up to a total of 32. The P2D

descriptor types satisfy different needs for various software

models.

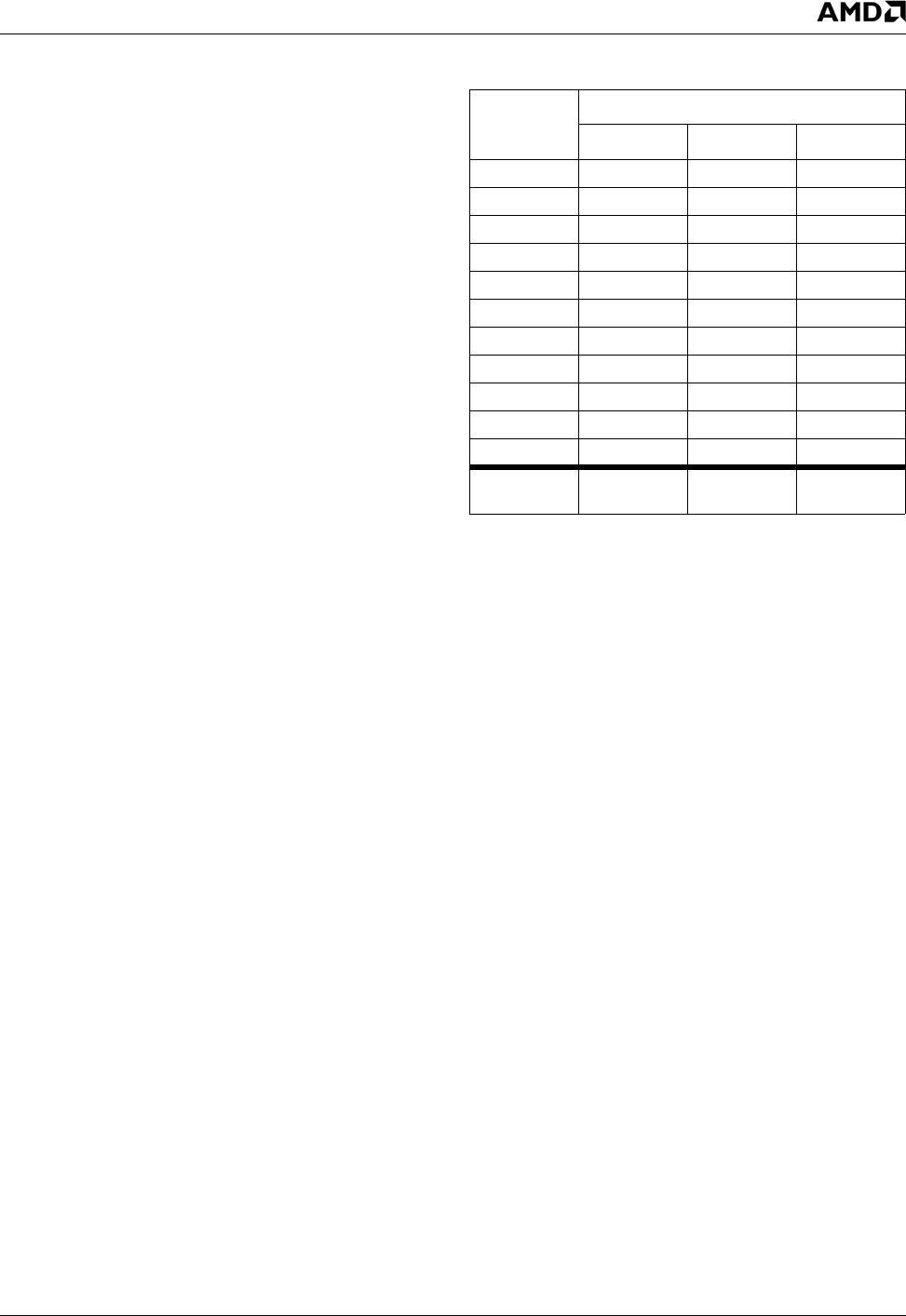

Table 4-2. MSR Mapping

Destination

Source (Note 1)

Note 1. The xxxx contains the lower two bits of the 18 bits from

the port fields plus the 14-bit MSR offset.

CPU Core GLCP GLPCI

CPU Core 0000xxxxh 2C00xxxxh 2C00xxxxh

GLIU0 1000xxxxh 2000xxxxh 2000xxxxh

GLMC 2000xxxxh 2400xxxxh 2400xxxxh

GLIU1 4000xxxxh 1000xxxxh 1000xxxxh

GLCP 4C00xxxxh 0000xxxxh 6000xxxxh

GLPCI 5000xxxxh 8000xxxxh 0000xxxxh

DC 8000xxxxh 3000xxxxh 3000xxxxh

GP A000xxxxh 3400xxxxh 3400xxxxh

VP 4800xxxxh 4000xxxxh 3800xxxxh

VIP 5400xxxxh

Security Block 5800xxxxh

Companion

Device

51Y0xxxxh

(Note 2)

Note 2. Y is the hex value obtained from one bit (always a 0) plus

the port number (#) of the six port field addresses [0+#].

Example: # = 5, therefore the Y value is [0+101] which is

5h, thus the address = 5150xxxxh.

8ZK0xxxxh

(Note 3)

Note 3. ZK are the hex values obtained from the concatenation

of [10+#+000], where # is the port number from the six

port field address. Example # = 5, the ZK value is

[10+101+000] which is [1010,1000]. In hex. it is A8h; thus

the address is 8A80xxxxh.

NA