AMD Geode™ LX Processors Data Book 349

Display Controller Register Descriptions

33234H

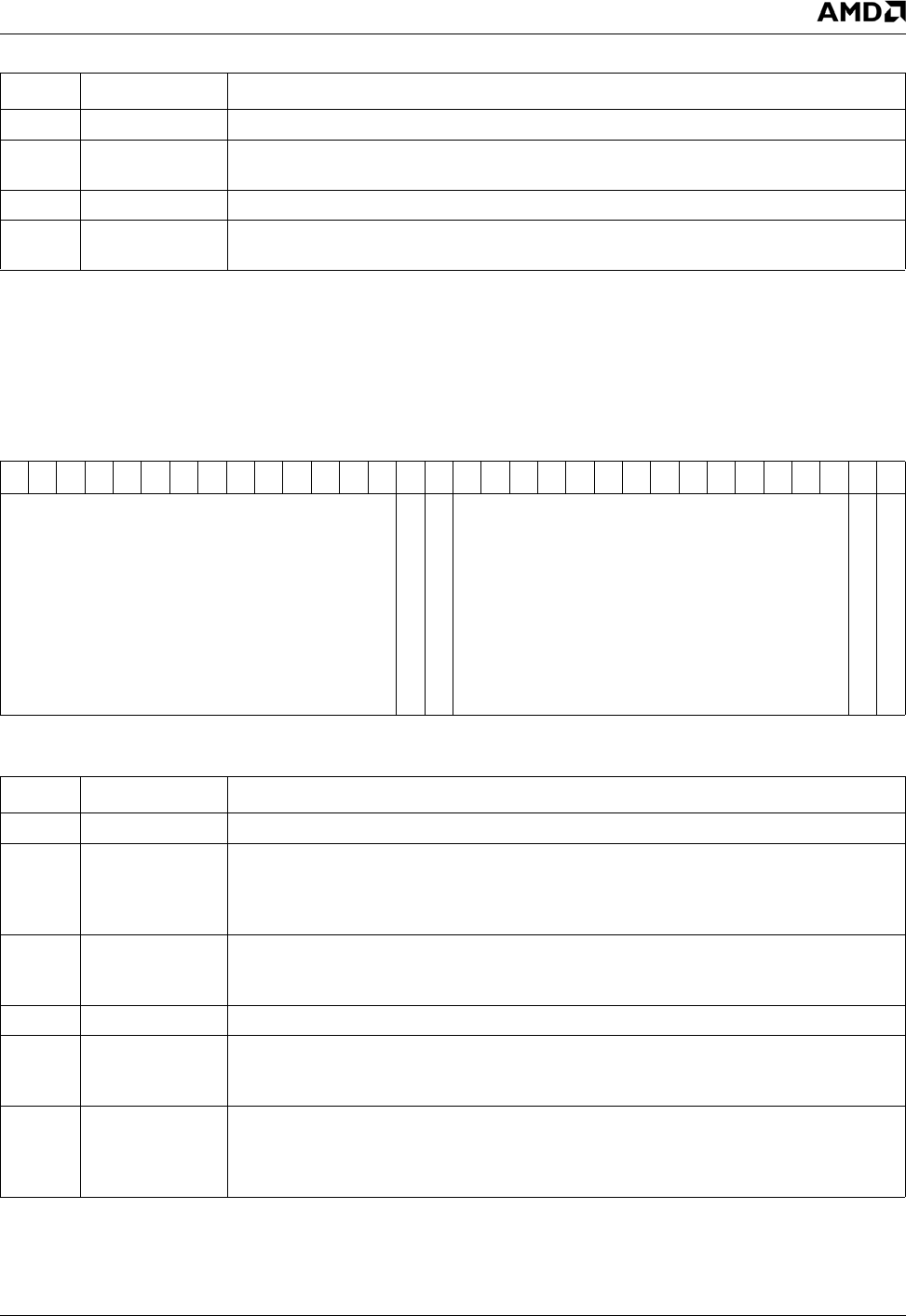

6.6.12.5 DC Interrupt (DC_IRQ)

DC_CLR_KEY_Y Bit Descriptions

Bit Name Description

31:27 RSVD Reserved. Set to 0.

26:16 CLR_KEY_Y_

END

Color Key Vertical End. This field represents the vertical end position of the color key

region minus 1. This represents the first line past the end of the color key region.

15:11 RSVD Reserved. Set to 0.

10:0 CLR_KEY_Y_

START

Color Key Vertical Start. This field represents the vertical start position of the color key

region minus 1. This represents the first line within the color key region.

DC Memory Offset 0C8h

Typ e R /W

Reset Value 00000003h

DC_IRQ Register Map

313029282726252423222120191817161514131211109876543210

RSVD

VIP_VSYNC_LOSS_IRQ

IRQ

RSVD

VIP_VSYNC_LOSS_IRQ_MASK

IRQ_MASK

DC_IRQ Bit Descriptions

Bit Name Description

31:18 RSVD Reserved. Set to 0.

17 VIP_VSYNC_

LOSS_IRQ

VIP VSYNC Loss IRQ. If set to 1, this field indicates that while GenLock was enabled,

GenLock timeout was enabled, and the DC reached the end of a frame and detected

VIP_VIDEO_OK (DC Memory Offset D4h[23]) inactive. As a result of this condition, the

DC began display of a field/frame based on its own timings.

16 IRQ IRQ Status. If set to 1, this field indicates that the vertical counter has reached the value

set in the IRQ/Filter Control Register. The state of the IRQ_MASK, bit 0, will not prevent

this bit from being set. To clear the interrupt, write a 1 to this bit.

15:2 RSVD Reserved. Set to 0.

1 VIP_VSYNC_

LOSS_IRQ_

MASK

VIP VSYNC Loss IRQ Mask. Masks generation of an interrupt in the event that the DC

reaches the end of a frame with GenLock enabled and GenLock timeout enabled and

determines that the VIP_VIDEO_OK (DC Memory Offset D4h[23]) input is inactive.

0 IRQ_MASK IRQ Mask. Setting this bit to 1 prevents the Display Controller from generating an inter-

rupt signal when the vertical counter reaches the value programmed in

DC_IRQ_FILT_CTL (DC Memory Offset 094h). Clearing this bit disables interrupt gener-

ation, but will NOT prevent IRQ, bit 16, from being set.