58 AMD Geode™ LX Processors Data Book

GLIU Register Descriptions

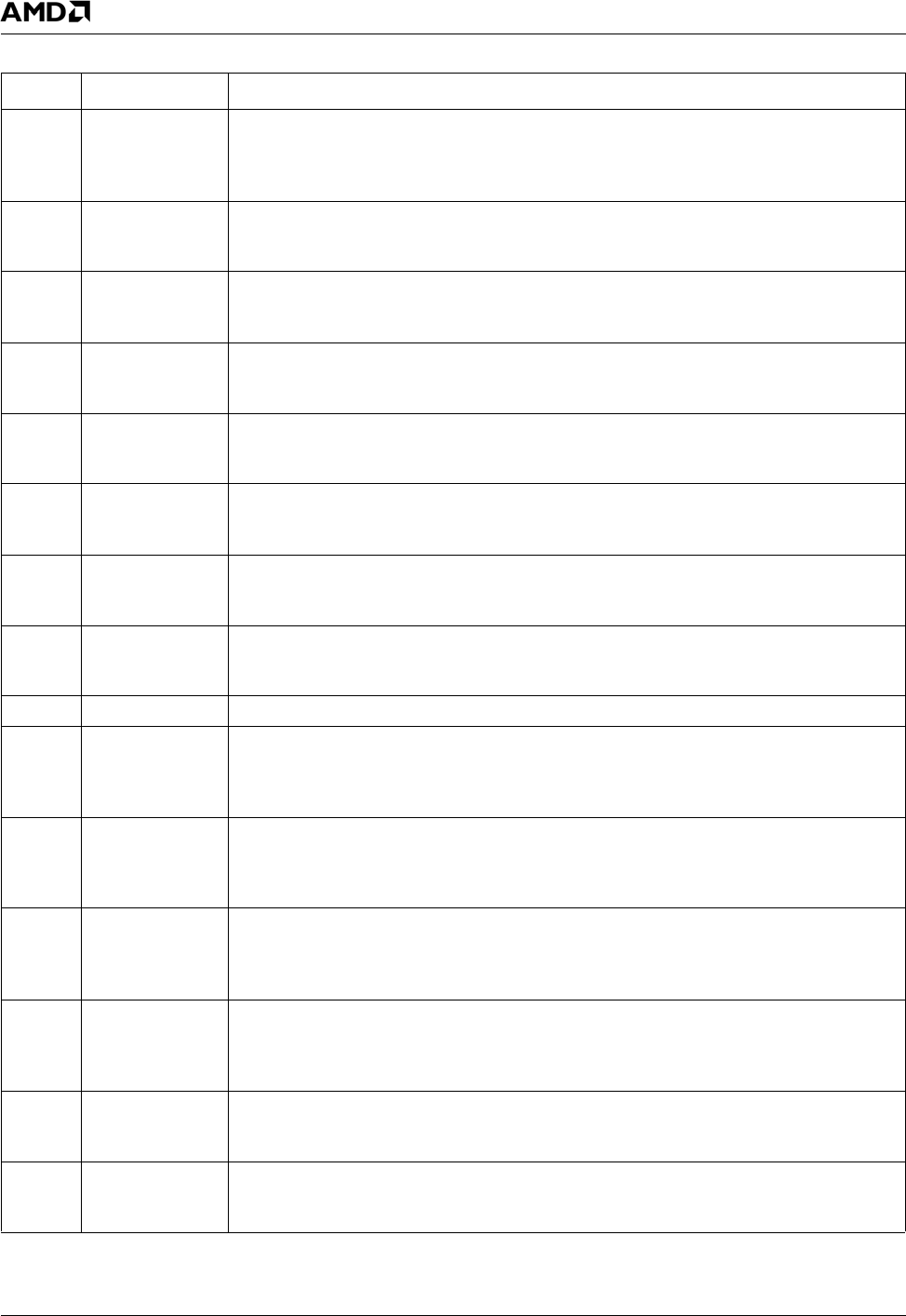

33234H

39 EFLAG7 Request Comparator Error Flag 0. If high, records that an ERR was generated due to a

Request Comparator 0 (RQ_COMPARE_VAL0, GLIU0 MSR 100000C0h, GLIU1 MSR

400000C0h) event. Write 1 to clear; writing 0 has no effect. EMASK7 (bit 7) must be low

to generate ERR and set flag.

38 EFLAG6 Statistic Counter Error Flag 3. If high, records that an ERR was generated due to a

Statistic Counter 3 (GLIU0 MSR 100000ACh, GLIU1 MSR 400000ACh) event. Write 1 to

clear; writing 0 has no effect. EMASK6 (bit 6) must be low to generate ERR and set flag.

37 EFLAG5 Statistic Counter Error Flag 2. If high, records that an ERR was generated due to a

Statistic Counter 2 (GLIU0 MSR 100000A8h, GLIU1 MSR 400000A8h) event. Write 1 to

clear; writing 0 has no effect. EMASK5 (bit 5) must be low to generate ERR and set flag.

36 EFLAG4 Statistic Counter Error Flag 1. If high, records that an ERR was generated due to a

Statistic Counter 1 (GLIU0 MSR 100000A4h, GLIU1 MSR 400000A4h) event. Write 1 to

clear; writing 0 has no effect. EMASK4 (bit 4) must be low to generate ERR and set flag.

35 EFLAG3 Statistic Counter Error Flag 0. If high, records that an ERR was generated due to a

Statistic Counter 0 (GLIU0 MSR 100000A0h, GLIU1 MSR 400000A0h) event. Write 1 to

clear; writing 0 has no effect. EMASK3 (bit 3) must be low to generate ERR and set flag.

34 EFLAG2 Unhandled SMI Error Flag. If high, records that an ERR was generated due an unhan-

dled SSMI (synchronous error). Write 1 to clear; writing 0 has no effect. EMASK2 (bit 2)

must be low to generate ERR and set flag Unhandled SMI.

33 EFLAG1 Unexpected Address Error Flag. If high, records that an ERR was generated due an

unexpected address (synchronous error). Write 1 to clear; writing 0 has no effect.

EMASK1 (bit 1) must be low to generate ERR and set flag.

32 EFLAG0 Unexpected Type Error Flag. If high, records that an ERR was generated due an unex-

pected type (synchronous error). Write 1 to clear; writing 0 has no effect. EMASK0 (bit 0)

must be low to generate ERR and set flag.

31:15 RSVD Reserved.

14 EMASK14 Data Comparator Error Mask 3. Write 0 to enable EFLAG14 (bit 46) and to allow a Data

Comparator 3 (DA_COMPARE_VAL_LO3/DA_COMPARE_VAL_HI3, GLIU0 MSR

100000DCh/100000DDh, GLIU1 MSR 400000DCh/400000DDh) event to generate an

ERR and set flag.

13 EMASK13 Data Comparator Error Mask 2. Write 0 to enable EFLAG13 (bit 45) and to allow a Data

Comparator 2 (DA_COMPARE_VAL_LO2/DA_COMPARE_VAL_HI2, GLIU0 MSR

100000D8h/100000D9h, GLIU1 MSR 400000D8h/400000D9h) event to generate an

ERR and set flag.

12 EMASK12 Data Comparator Error Mask 1. Write 0 to enable EFLAG12 (bit 44) and to allow a Data

Comparator 1 (DA_COMPARE_VAL_LO1/DA_COMPARE_VAL_HI1, GLIU0 MSR

100000D4h/100000D5h, GLIU1 MSR 400000D4h/400000D5h) event to generate an

ERR and set flag.

11 EMASK11 Data Comparator Error Mask 0. Write 0 to enable EFLAG11 (bit 43) and to allow a Data

Comparator 0 (DA_COMPARE_VAL_LO0/DA_COMPARE_VAL_HI0, GLIU0 MSR

100000D4h/100000D5h, GLIU1 MSR 400000D4h/400000D5h) event to generate an

ERR and set flag.

10 EMASK10 Request Comparator Error Mask 3. Write 0 to enable EFLAG10 (bit 42) and to allow a

Request Comparator 3 (RQ_COMPARE_VAL3, GLIU0 MSR 100000C6h, GLIU1 MSR

400000C6h) event to generate an ERR

9 EMASK9 Request Comparator Error Mask 2. Write 0 to enable EFLAG9 (bit 41) and to allow a

Request Comparator 2 (RQ_COMPARE_VAL2, GLIU0 MSR 100000C4h, GLIU1 MSR

400000C4h) event to generate an ERR.

GLD

_MSR_ERROR Bit Descriptions (Continued)

Bit Name Description