156 AMD Geode™ LX Processors Data Book

CPU Core Register Descriptions

33234H

5.5.2.59 L1 Instruction TLB Least Recently Used MSR (ITB_LRU_MSR)

MSR Address 00001721h

Typ e R /W

Reset Value 00000000_00000000h

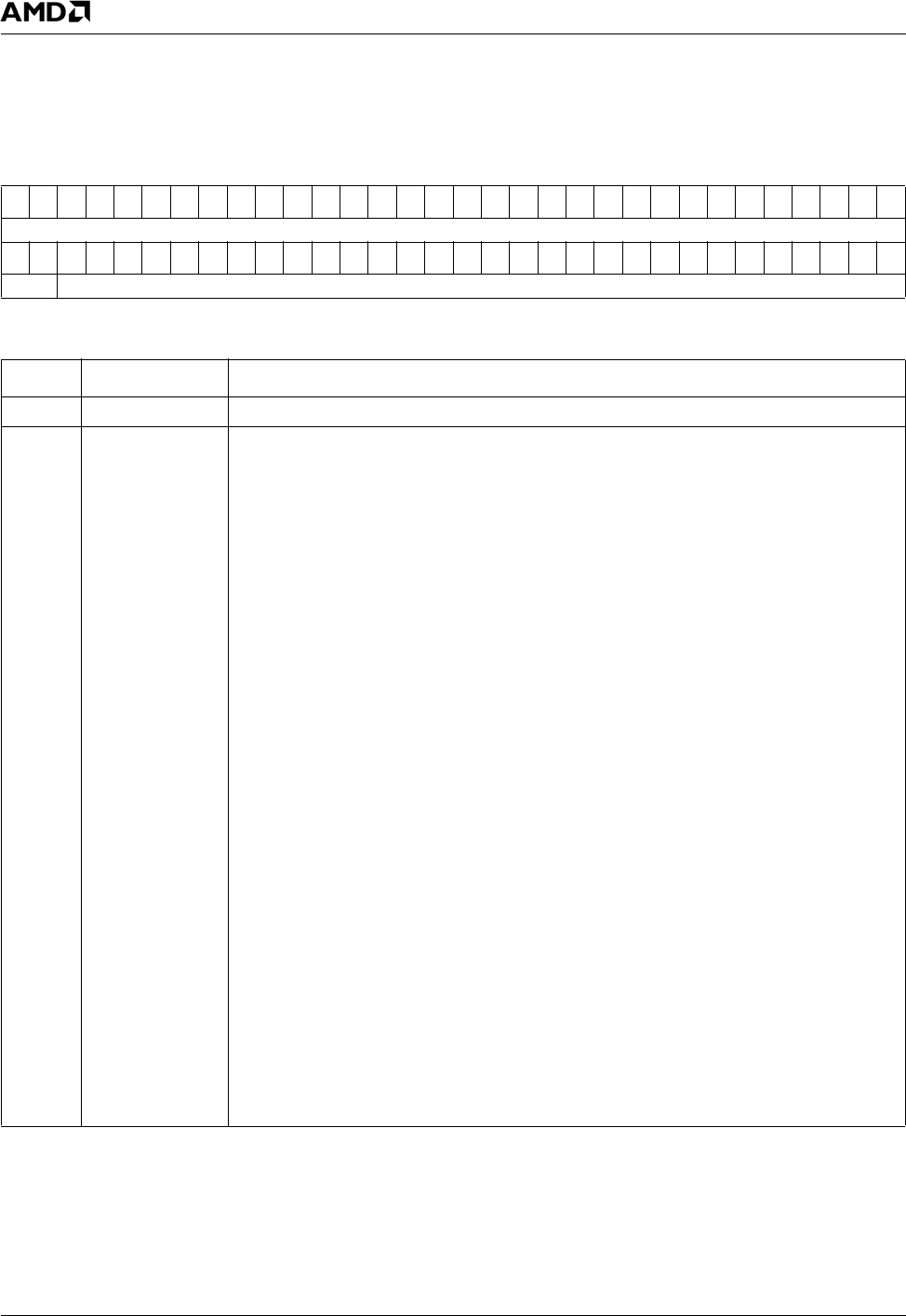

ITB_LRU_MSR Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

313029282726252423222120191817161514131211109876543210

RSVD LRU

ITB_LRU_MSR Bit Descriptions

Bits Name Description

63:30 RSVD (RO) Reserved (Read Only). (Default = 0)

29:0 LRU Least Recently Used Value.

Bit 29: Entries 8-11 more recent than entries 12-15

Bit 28: Entries 4-7 more recent than entries 12-15

Bit 27: Entries 4-7 more recent than entries 8-11

Bit 26: Entries 0-3 more recent than entries 12-15

Bit 25: Entries 0-3 more recent than entries 8-11

Bit 24: Entries 0-3 more recent than entries 4-7

Bit 23: Entry 14 more recent than entry 15

Bit 22: Entry 13 more recent than entry 15

Bit 21: Entry 13 more recent than entry 14

Bit 20: Entry 12 more recent than entry 15

Bit 19: Entry 12 more recent than entry 14

Bit 18: Entry 12 more recent than entry 13

Bit 17: Entry 10 more recent than entry 11

Bit 16: Entry 9 more recent than entry 11

Bit 15: Entry 9 more recent than entry 10

Bit 14: Entry 8 more recent than entry 11

Bit 13: Entry 8 more recent than entry 10

Bit 12: Entry 8 more recent than entry 9

Bit 11: Entry 6 more recent than entry 7

Bit 10: Entry 5 more recent than entry 7

Bit 9: Entry 5 more recent than entry 6

Bit 8: Entry 4 more recent than entry 7

Bit 7: Entry 4 more recent than entry 6

Bit 6: Entry 4 more recent than entry 5

Bit 5: Entry 2 more recent than entry 3

Bit 4: Entry 1 more recent than entry 3

Bit 3: Entry 1 more recent than entry 2

Bit 2: Entry 0 more recent than entry 3

Bit 1: Entry 0 more recent than entry 2

Bit 0: Entry 0 more recent than entry 1

0: False (Default)

1: True