500 AMD Geode™ LX Processors Data Book

Video Input Port Register Descriptions

33234H

6.10.2.14 VIP Task A U Offset (VIP_TASK_A_U_OFFSET)

6.10.2.15 VIP Task B Video Even Base/Horizontal End (VIP_TASK_B_VID_EVEN_BASE_HORIZ_END)

VIP Memory Offset 34h

Typ e R /W

Reset Value 00000000h

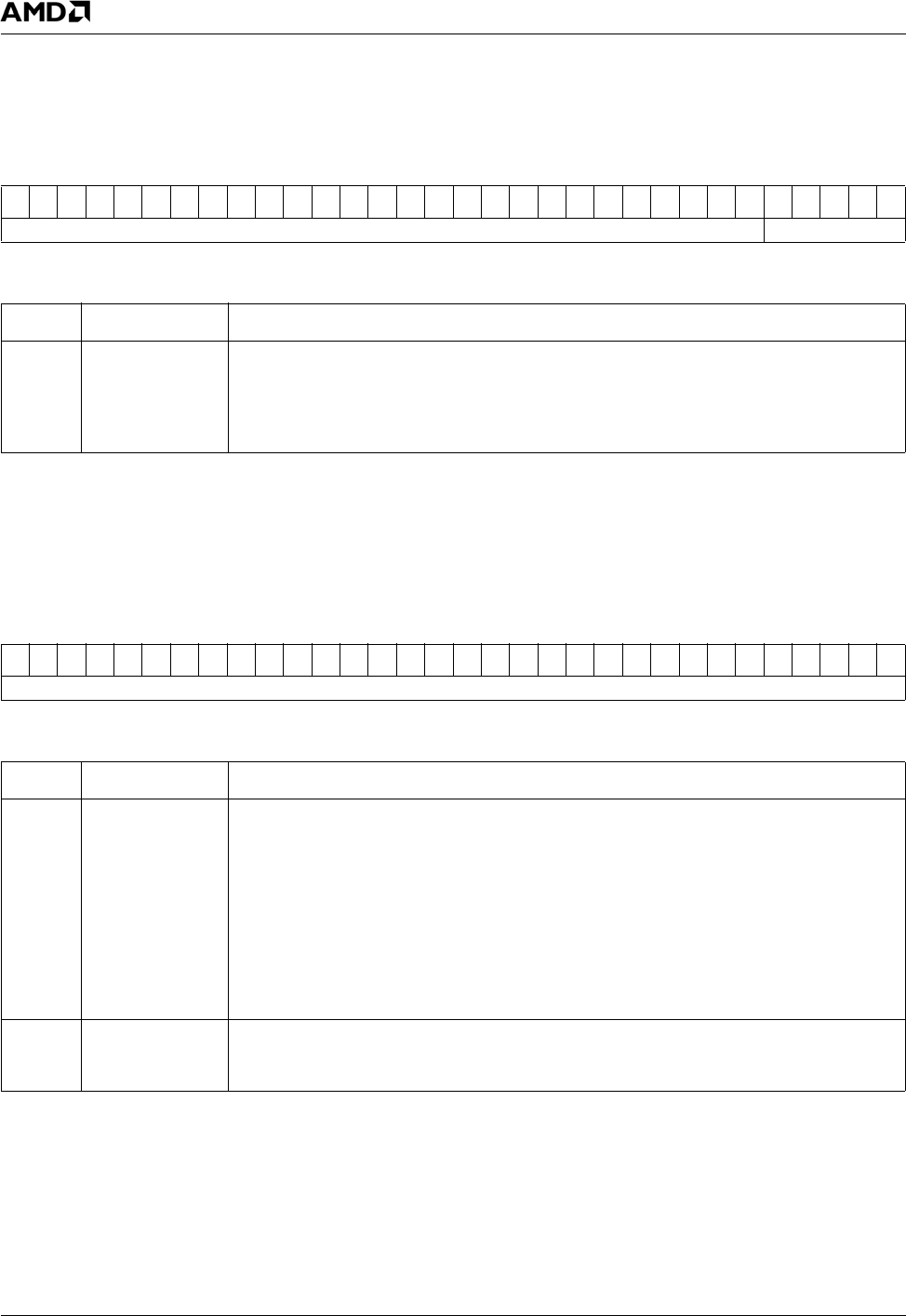

VIP_TASK_A_U_OFFSET Register Map

313029282726252423222120191817161514131211109876543210

Task A U Odd Offset Program to 00000

VIP_TASK_A_U_OFFSET Bit Descriptions

Bit Name Description

31:0 Task A U Odd

Offset

Task A U Odd Offset. This register determines the starting address of the U buffer when

data is stored in planar format. For interlaced input, this register will determine the start-

ing address of the U data for the odd field. The start of the U buffer is determined by add-

ing the contents of this register to that of the base address. This value needs to be 32-

byte aligned. (Bits [4:0] are required to be 00000.)

VIP Memory Offset 38h

Typ e R /W

Reset Value 00000000h

VIP_TASK_B_VID_EVEN_BASE_HORIZ_END Register Map

313029282726252423222120191817161514131211109876543210

TASK_B_VID_EVEN_BASE_HORIZ_END (601 type modes)

VIP_TASK_B_VID_EVEN_BASE_HORIZ_END Bit Descriptions

Bit Name Description

31:0 TASK_B_VID_

EVEN_BASE

Task B Video Even Base Address. This register specifies the base address in graphics

memory where even video field data are stored. Changes to this register take effect at

the beginning of the next field. The value in this register is 16-byte aligned. Bits [3:0] are

always 0, and define the required address space.

Note: This register is double buffered. When a new value is written to this register, the

new value is placed in a special pending register, and the Base Register Not

Updated bit (VIP Memory Offset 08h[16]) is set to 1. The Task B Video Even

Base Address register is not updated at this point. When the first data of the next

field is captured, the pending values of all base registers are written to the appro-

priate base registers, and the Base Register Not Updated bit is cleared.

15:0 HORIZ_END Horizontal End. This register is redefined in BT.601 mode. In BT. 601 type input modes

timing is derived from the external HSYNC and VSYNC inputs. This value specifies

where video data ends for the line.