10.4.3ARMBootModeConfiguration

www.ti.com

DefaultDeviceConfigurations

Thedeviceconfigurationpins(BTMODE[3:0])determinewhethertheARMbootsfromitsROMorfromthe

asynchronousEMIF(EMIFA).

WhenROMbootisselected(BTMODE[3:0]!=0100),ajumptotheinternalTCMROM(00008000h)is

forcedintothefirstfetchedinstructionword.TheembeddedROMbootloader(RBL)codethenperforms

certainconfigurationsteps,readsthebootconfigurationregister(BOOTCFG)intheSystemModuleto

determinethedesiredbootmethod,andbranchestoanappropriatesecondaryloaderutility.

IfEMIFAbootisselected(BTMODE[3:0]=0100),ajumptothehighestbranchaddress(02000000h)is

forcedintothefirstfetchedinstructionword.ARMInstructionAddressModificationlogicinsertsa1onbit

30oftheaddressbustomodifytheaccesstoaddress42000000h,whichisthestartoftheEMIFACS2

memoryregion.TheARMthencontinuesexecutingfromexternalmemoryusingthedefaultEMIFA

timingsuntilmodifiedbysoftware.CodewithintheEMIFAmemoryshouldexecuteabranchtotheactual

EMIFAaddress,andthendisabletheInstructionAddressModificationlogicbyclearingtheADDRMODbit

intheARMbootconfigurationregister(ARMBOOT)intheSystemModule.

Note:EitherNORFlashorROMmustbeconnectedtothefirstEMIFAchipselectspace

(EM_CS2).TheEMIFAdoesnotsupportdirectexecutionfromNANDFlash.

TheARMbootconfigurationregister(ARMBOOT)isusedtocontroltheARM926boot.TheARMBOOT

valuedoesnotchangeasaresultofaglobalsoftreset,insteadthelastvaluewrittenisretained.

ARMBOOTisshowninFigure10-2anddescribedinTable10-4.Seedevice-specificdatamanualfor

detailsonARMBOOT.

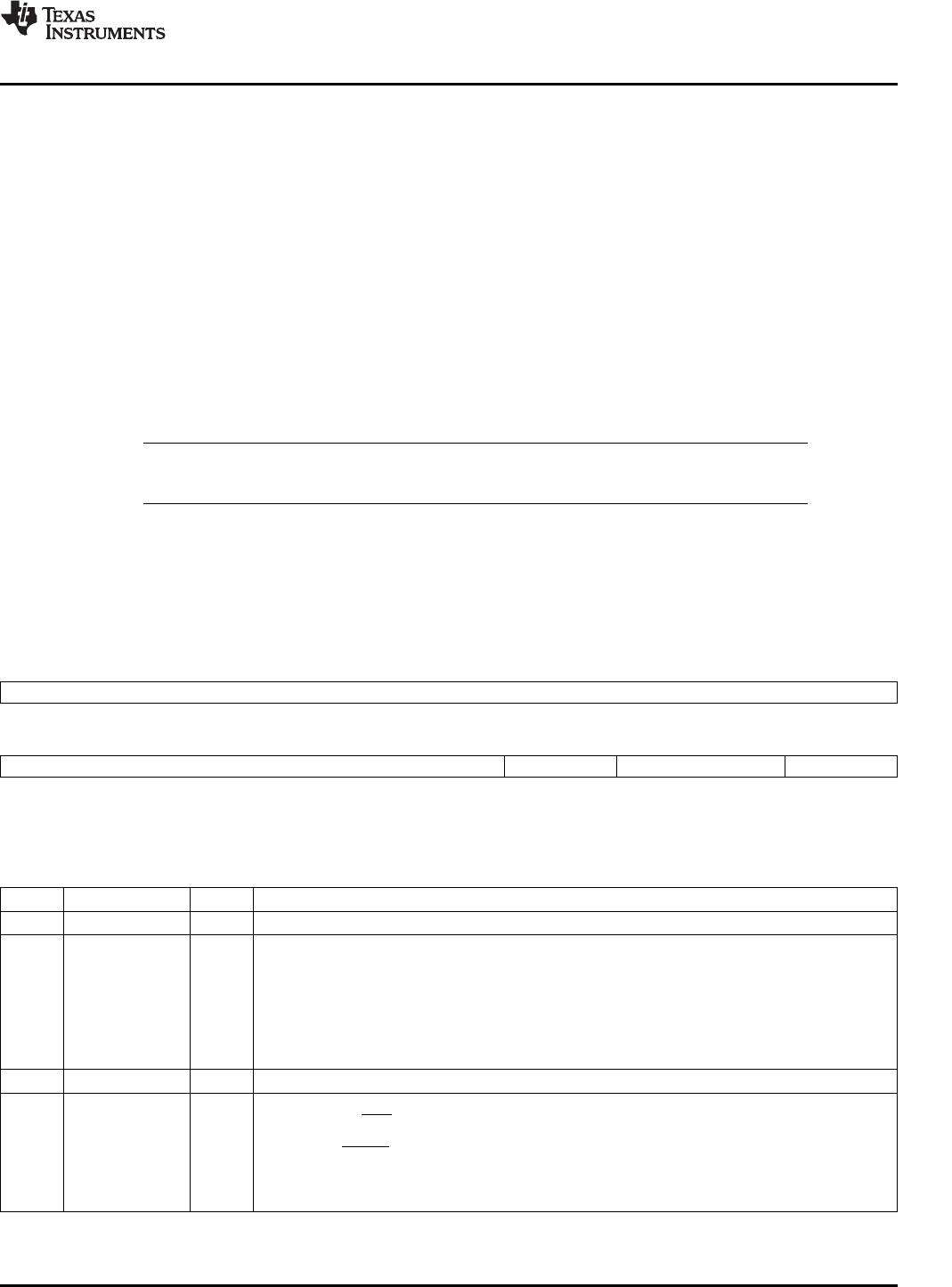

Figure10-2.ARMBootConfigurationRegister(ARMBOOT)

3116

Reserved

R-0

1554310

ReservedADDRMODReservedTRAMBOOT

R-0R/W-CR-0R/W-0

LEGEND:R/W=Read/Write;R=Readonly;C=Clear;-n=valueafterreset

Table10-4.ARMBootConfigurationRegister(ARMBOOT)FieldDescriptions

BitFieldValueDescription

31-5Reserved0Reserved.Readreturns0.

4ADDRMODIAHBAddressModification.ThedefaultvalueforthisbitisdeterminedbytheBOOTMODE

configurationbits(BTMODE[3:0]).IfBTMODE[3:0]=0100[EMIFAdirectboot(ROM/NOR)],then

ADDRMODdefaultsto1sothatinstructionfetchesfromtheARMpointtoEMIFACS2memory

space.ForallotherBTMODE[3:0]values,ADDRMODdefaultsto0sotheARMbootsfromitsTCM

(ROMorRAM).

0Noaddressmodification.

1Addressbit30istiedhightomodifyIAHBfetchaddresstopointtoEMIFA.

3-1Reserved0Reserved.Readreturns0.

0TRAMBOOTARMTCMRAMBoot.Thisisa"sticky"bitthatcanbeusedtoforcetheARM926tobootfrom

ITCMRAM.OnPORreset,thisbitisinitializedto0becauseTCMRAMisnotinitialized;otherwise,

thebitretainsthevalue.AfterinitializingITCMRAM,softwarecansetthisbitsothatsubsequent

Warmreset(RESET)orsoftresetbootsfromtheITCM.

0UseBTMODE[3:0]selectedbootmode

1BootfromITCMRAM

SPRUEP9A–May2008Reset117

SubmitDocumentationFeedback