5.4.11PLLControllerClockAlignControlRegister(ALNCTL)

PLLControllerRegisterMap

www.ti.com

ThePLLcontrollerclockaligncontrolregister(ALNCTL)isshowninFigure5-14anddescribedin

Table5-15.IndicateswhichSYSCLKsneedtobealignedforproperdeviceoperation.

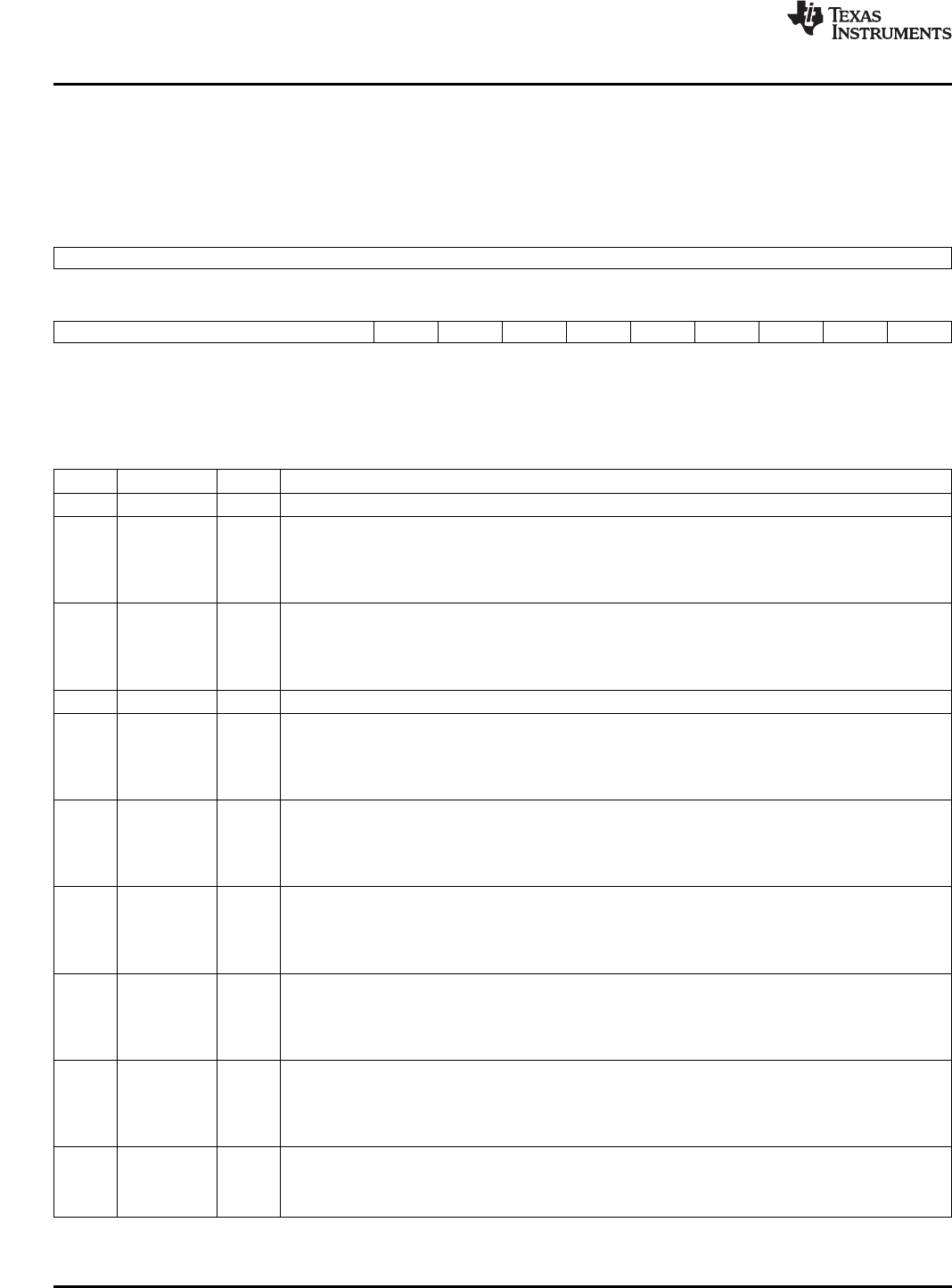

Figure5-14.PLLControllerClockAlignControlRegister(ALNCTL)

3116

Reserved

R-0

159876543210

ReservedALN9

(1)

ALN8

(1)

RsvdALN6

(1)

ALN5

(1)

ALN4

(1)

ALN3

(1)

ALN2

(1)

ALN1

R-0R/W-1R/W-1R-0R/W-1R/W-1R/W-1R/W-1R/W-1R/W-1

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

(1)

ForPLL1only,notsupportedforPLL2.

Table5-15.PLLControllerClockAlignControlRegister(ALNCTL)FieldDescriptions

BitFieldValueDescription

31-9Reserved0Reserved

8ALN9SYSCLK9needstobealignedtoothersselectedinthisregister.ForPLL1only,notsupportedfor

PLL2.

0No

1Yes

7ALN8SYSCLK8needstobealignedtoothersselectedinthisregister.ForPLL1only,notsupportedfor

PLL2.

0No

1Yes

6Reserved0Reserved

5ALN6SYSCLK6needstobealignedtoothersselectedinthisregister.ForPLL1only,notsupportedfor

PLL2.

0No

1Yes

4ALN5SYSCLK5needstobealignedtoothersselectedinthisregister.ForPLL1only,notsupportedfor

PLL2.

0No

1Yes

3ALN4SYSCLK4needstobealignedtoothersselectedinthisregister.ForPLL1only,notsupportedfor

PLL2.

0No

1Yes

2ALN3SYSCLK3needstobealignedtoothersselectedinthisregister.ForPLL1only,notsupportedfor

PLL2.

0No

1Yes

1ALN2SYSCLK2needstobealignedtoothersselectedinthisregister.ForPLL1only,notsupportedfor

PLL2.

0No

1Yes

0ALN1SYSCLK1needstobealignedtoothersselectedinthisregister.

0No

1Yes

PLLController 54SPRUEP9A–May2008

SubmitDocumentationFeedback