6.6.1PeripheralRevisionandClassInformationRegister(PID)

6.6.2InterruptEvaluationRegister(INTEVAL)

PSCRegisters

www.ti.com

Theperipheralrevisionandclassinformation(PID)registerisshowninFigure6-3anddescribedin

Table6-7.

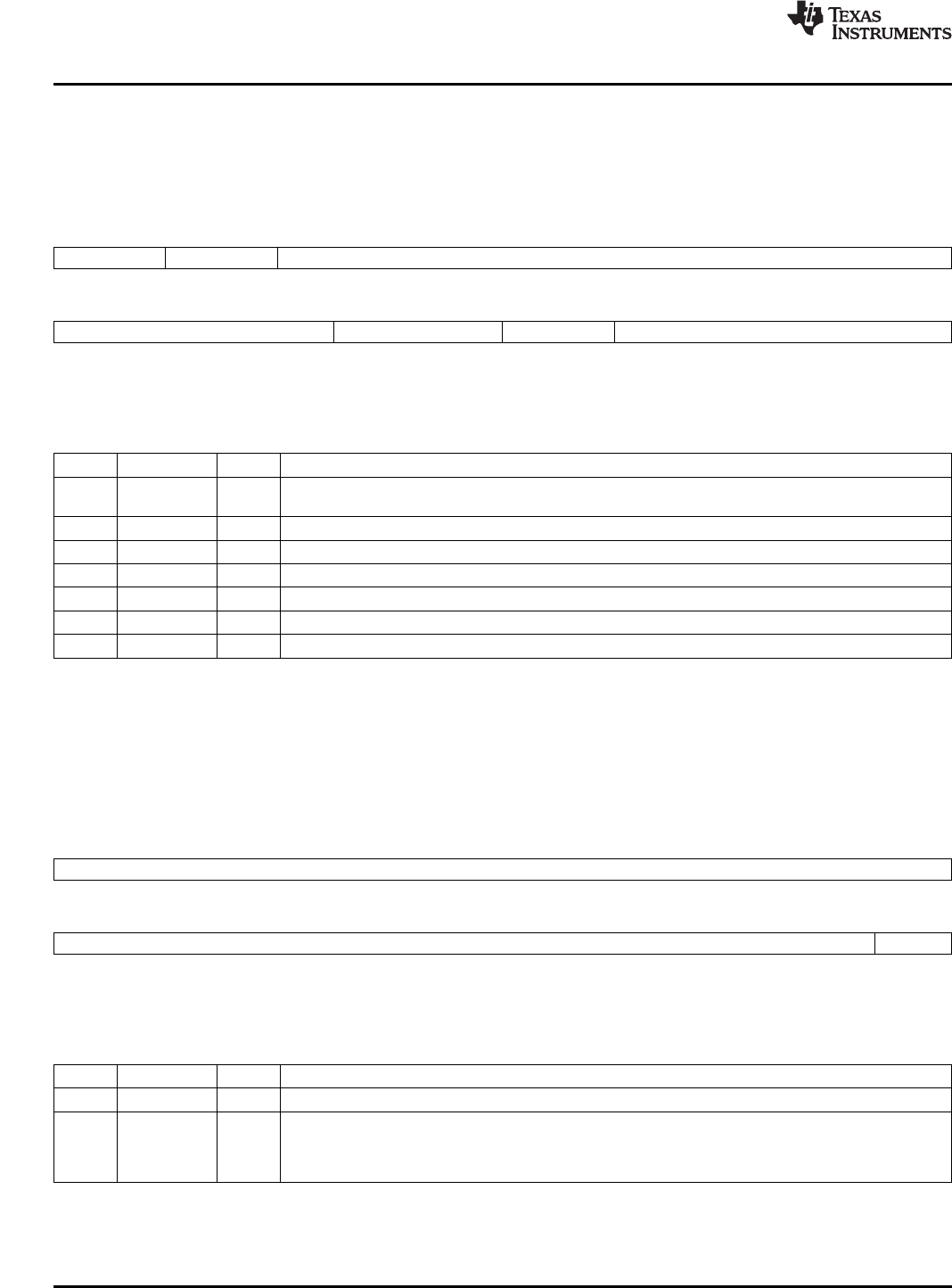

Figure6-3.PeripheralRevisionandClassInformationRegister(PID)

313029282716

SCHEMEReservedFUNC

R-1R-0R-482h

15111087650

RTLMAJORCUSTOMMINOR

R-3hR-1R-0R-5h

LEGEND:R=Readonly;-n=valueafterreset

Table6-7.PeripheralRevisionandClassInformationRegister(PID)FieldDescriptions

BitFieldValueDescription

31-30SCHEME0-3hDistinguishesbetweentheoldschemeandthecurrentscheme.Thereisasparebittoencodefuture

schemes.

29-28Reserved0Reserved

27-16FUNC0-FFFhIndicatesasoftwarecompatiblemodulefamily.

15-11RTL0-1FhRTLVersion.

10-8MAJOR0-7hMajorRevision.

7-6CUSTOM0-3hIndicatesaspecialversionforaparticulardevice.

5-0MINOR0-3FhMinorRevision.

Theinterruptevaluationregister(INTEVAL)isshowninFigure6-4anddescribedinTable6-8.

Figure6-4.InterruptEvaluationRegister(INTEVAL)

3116

Reserved

R-0

1510

ReservedALLEV

R-0W-0

LEGEND:R=Readonly;W=Writeonly;-n=valueafterreset

Table6-8.InterruptEvaluationRegister(INTEVAL)FieldDescriptions

BitFieldValueDescription

31-1Reserved0Reserved

0ALLEVEvaluatePSCinterrupt.

0Awriteof0hasnoeffect.

1Awriteof1re-evaluatestheinterruptcondition.

PowerandSleepController(PSC) 70SPRUEP9A–May2008

SubmitDocumentationFeedback