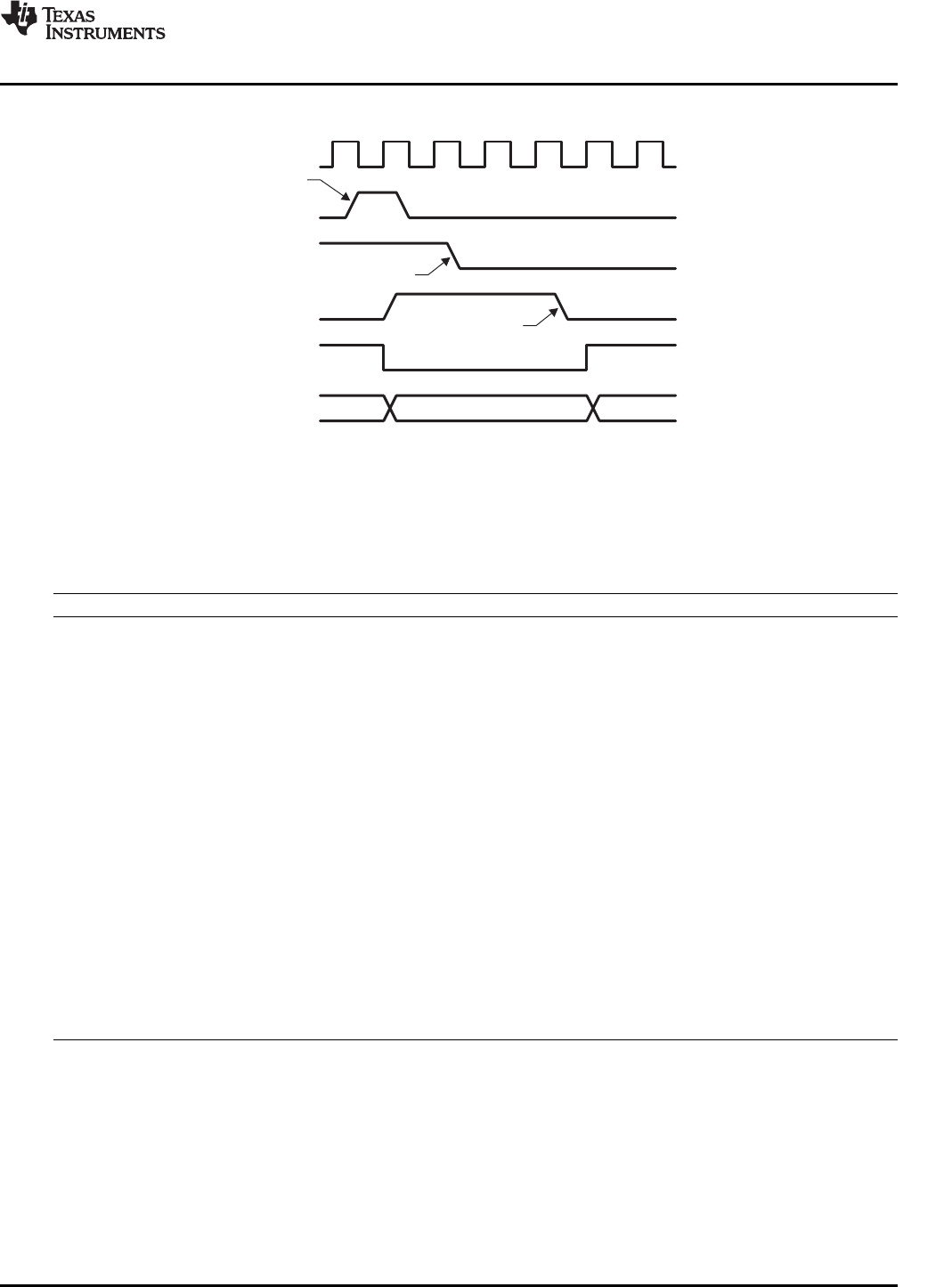

CLK

EABASE

VECTORn

EABASE

INTn

EINTn

IRQn/FIQn

IRQz/FIQz

ENTRY

Eventpulse

Disabled

Cleared

8.4AINTCRegisters

www.ti.com

AINTCRegisters

Figure8-4.DelayedInterruptDisable

Table8-2liststhememory-mappedregistersfortheAINTC.Seethedevice-specificdatamanualforthe

memoryaddressoftheseregisters.

Table8-2.ARMInterruptController(AINTC)Registers

OffsetAcronymRegisterDescriptionSection

00hFIQ0FastInterruptRequestStatusRegister0Section8.4.1

04hFIQ1FastInterruptRequestStatusRegister1Section8.4.2

08hIRQ0InterruptRequestStatusRegister0Section8.4.3

0ChIRQ1InterruptRequestStatusRegister1Section8.4.4

10hFIQENTRYFastInterruptRequestEntryAddressRegisterSection8.4.5

14hIRQENTRYInterruptRequestEntryAddressRegisterSection8.4.6

18hEINT0InterruptEnableRegister0Section8.4.7

1ChEINT1InterruptEnableRegister1Section8.4.8

20hINTCTLInterruptOperationControlRegisterSection8.4.9

24hEABASEInterruptEntryTableBaseAddressRegisterSection8.4.10

30hINTPRI0Interrupt0-7PriorityRegister0Section8.4.11

34hINTPRI1Interrupt8-15PriorityRegister1Section8.4.12

38hINTPRI2Interrupt16-23PriorityRegister2Section8.4.13

3ChINTPRI3Interrupt24-31PriorityRegister3Section8.4.14

40hINTPRI4Interrupt32-39PriorityRegister4Section8.4.15

44hINTPRI5Interrupt40-47PriorityRegister5Section8.4.16

48hINTPRI6Interrupt48-55PriorityRegister6Section8.4.17

4ChINTPRI7Interrupt56-63PriorityRegister7Section8.4.18

SPRUEP9A–May2008ARMInterruptController(AINTC)91

SubmitDocumentationFeedback