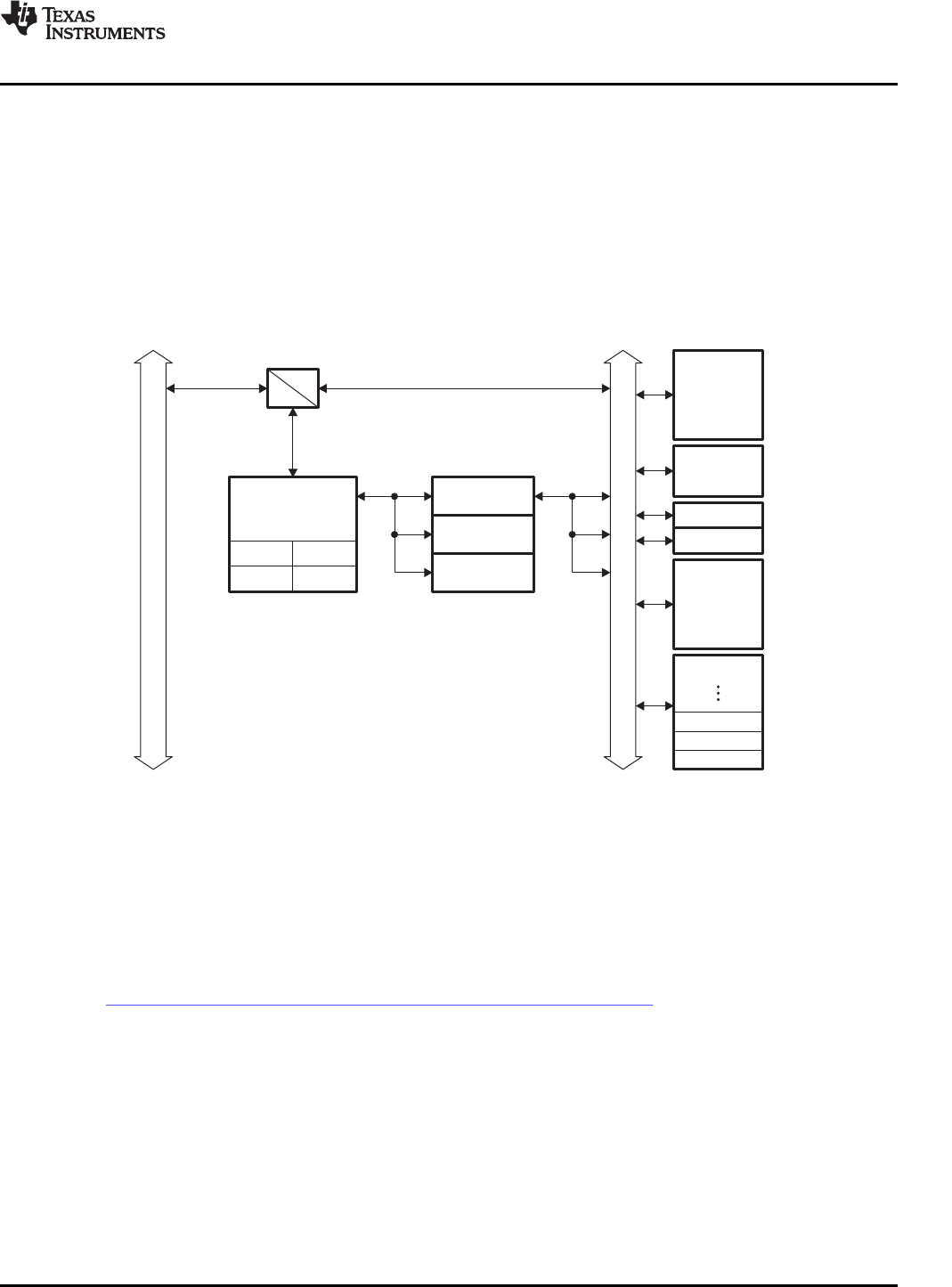

16KI$

8KD$

CP15

MMU

ARM926EJ-S

I-AHB

D-AHB

MasterI/F

16KRAM0

16KRAM1

8KROM

I-TCM

D-TCM

Slave-I/F

MasterI/F

DMA bus

ARM

interrupt

controller

(AINTC)

System

control

PLL0

PLL1

Power

sleep

controller

(PSC)

Peripherals

GFCbus

2.3References

www.ti.com

References

•VideoPortInterface(VPIF)

Figure2-1showsthefunctionalblockdiagramoftheDM646xDMSoCARMSubsystem.

TheDM646xDMSoCarchitectureusestwoprimarybussubsystemstotransferdatawithinthesystem:

•TheDMAbus(sometimescalleddatabus)isusedfordatatransferbetweensubsystemsand

modules.

•TheCFGbus(orconfigurationbus)isusedtoread/writetoperipheralregistersinvariousmodulesfor

configuration.

Figure2-1.TMS320DM646xDMSoCARMSubsystemBlockDiagram

SeethefollowingDM646xDMSoCrelateddocumentsformoreinformation:

•ForrelateddocumentationabouttheDM646xDMSoCotherthantheARMcore,seetheRelated

Documentationsectionatthebeginningofthisdocument.

•FormoredetailedinformationabouttheARMprocessorcore,seeARMLtd.’swebsite(particularly,

seetheARM926EJ-STechnicalReferenceManual):

–http://www.arm.com/documentation/ARMProcessor_Cores/index.html

SPRUEP9A–May2008ARMSubsystemOverview17

SubmitDocumentationFeedback