6.6.5ModuleErrorClearRegister0(MERRCR0)

6.6.6ModuleErrorClearRegister1(MERRCR1)

PSCRegisters

www.ti.com

Themoduleerrorclearregister0(MERRCR0)clearsthecorrespondinginterruptbitset(M[n])inthe

moduleerrorpendingregister0(MERRPR0)andthemodulestatusnregister(MDSTATn)interruptbit

fieldformodules0-31.MERRCR0isshowninFigure6-7anddescribedinTable6-11.

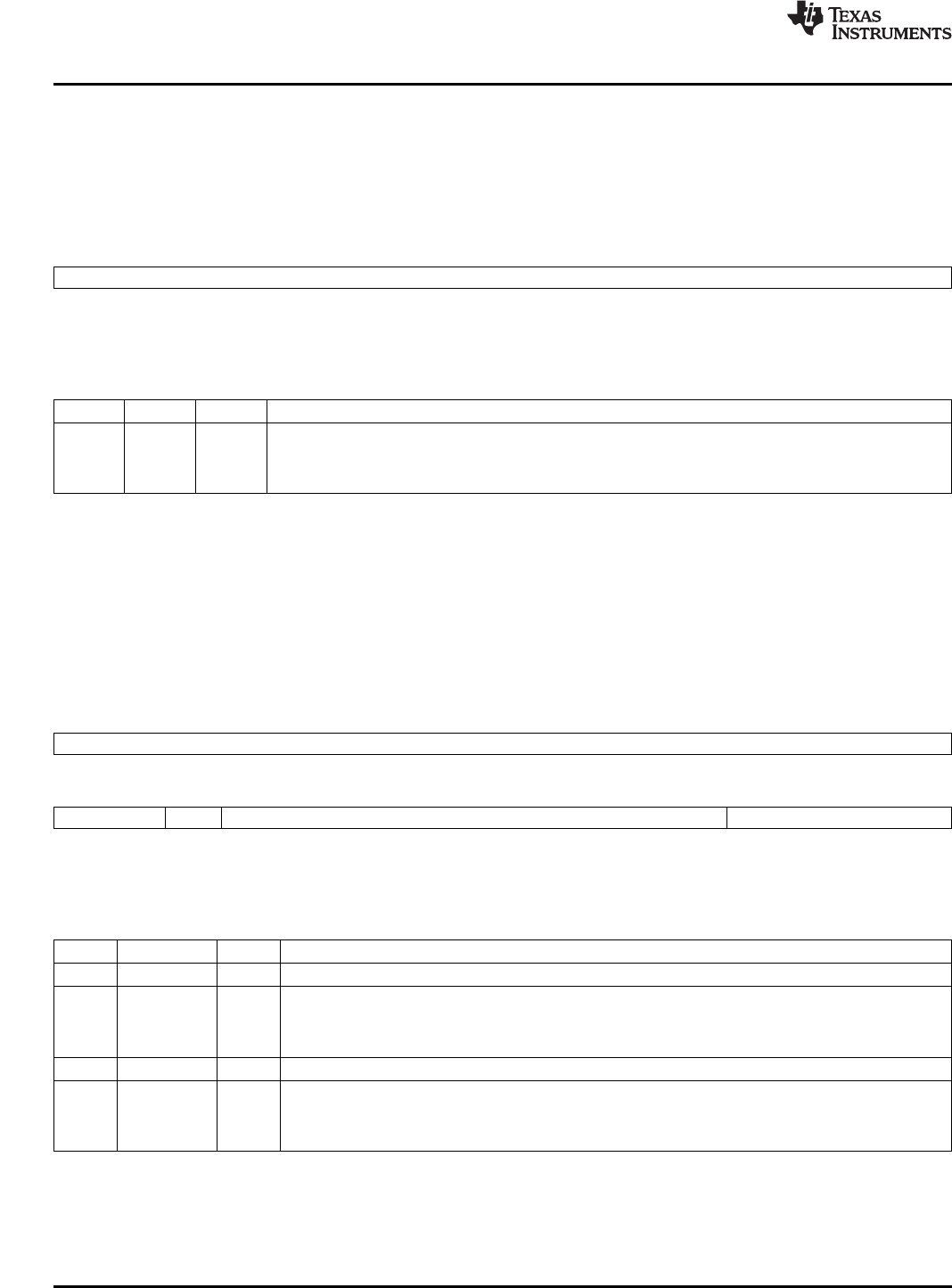

Figure6-7.ModuleErrorClearRegister0(MERRCR0)

310

M

W-0

LEGEND:W=Writeonly;-n=valueafterreset

Table6-11.ModuleErrorClearRegister0(MERRCR0)FieldDescriptions

BitFieldValueDescription

31-0M[n]Moduleinterruptclearbitformodules0-31.

0Awriteof0hasnoeffect.

1Clearsmoduleinterruptn.

Themoduleerrorclearregister1(MERRCR1)clearsthecorrespondinginterruptbitset(M[n])inthe

moduleerrorpendingregister1(MERRPR1)andthemodulestatusnregister(MDSTATn)interruptbit

fieldformodules32-45.MERRCR1isshowninFigure6-8anddescribedinTable6-12.

Figure6-8.ModuleErrorPendingRegister1(MERRCR1)

3116

Reserved

R-0

15141312430

ReservedMReservedM

R-0R-0R-0R-0

LEGEND:R=Readonly;-n=valueafterreset

Table6-12.ModuleErrorClearRegister1(MERRCR1)FieldDescriptions

BitFieldValueDescription

31-14Reserved0Reserved

13M[n]Moduleinterruptclearbitformodule45.

0Awriteof0hasnoeffect.

1Clearsmoduleinterruptn.

12-4Reserved0Reserved.(Modules36-44arereserved.SeeTable6-1.)

3-0M[n]Moduleinterruptclearbitformodules32-35.

0Awriteof0hasnoeffect.

1Clearsmoduleinterruptn.

72PowerandSleepController(PSC)SPRUEP9A–May2008

SubmitDocumentationFeedback