8.4.5FastInterruptRequestEntryAddressRegister(FIQENTRY)

8.4.6InterruptRequestEntryAddressRegister(IRQENTRY)

AINTCRegisters

www.ti.com

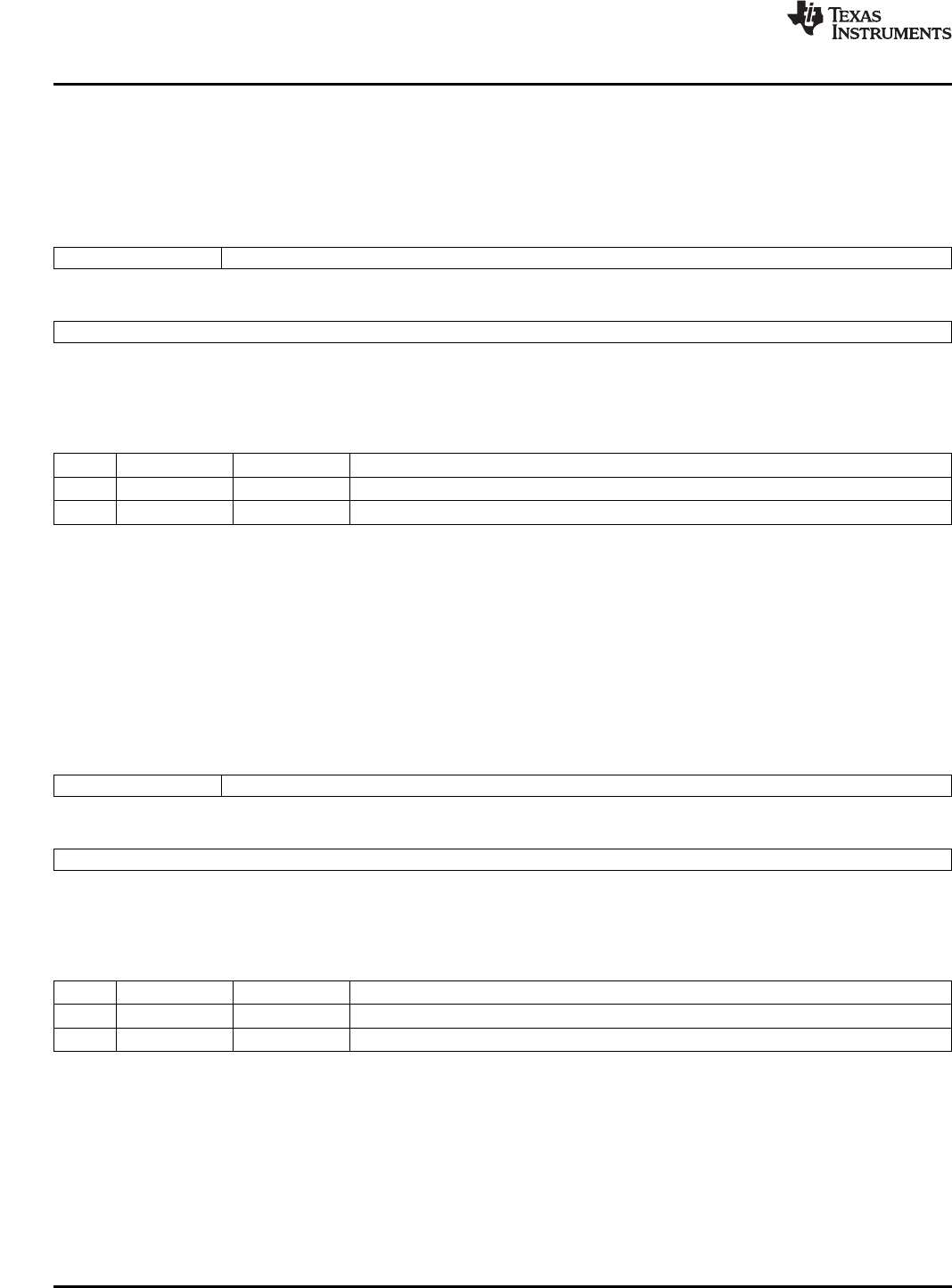

Thefastinterruptrequestentryaddressregister(FIQENTRY)isshowninFigure8-9anddescribedin

Table8-7.Entryaddress[28:0]forvalidFIQinterrupt.

Figure8-9.FastInterruptRequestEntryAddressRegister(FIQENTRY)

31292816

ReservedFIQENTRY

R-0R-0

150

FIQENTRY

R-0

LEGEND:R=Readonly;-n=valueafterreset

Table8-7.FastInterruptRequestEntryAddressRegister(FIQENTRY)FieldDescriptions

BitFieldValueDescription

31-29Reserved0Reserved

28-0FIQENTRY0-1FFFFFFFhInterruptentrytableaddressofthecurrenthighest-priorityfastinterruptrequest(FIQ).

Theinterruptrequestentryaddressregister(IRQENTRY)isshowninFigure8-10anddescribedin

Table8-8.Entryaddress[28:0]forvalidIRQinterrupt.

Figure8-10.InterruptRequestEntryAddressRegister(IRQENTRY)

31292816

ReservedIRQENTRY

R-0R-0

150

IRQENTRY

R-0

LEGEND:R=Readonly;-n=valueafterreset

Table8-8.InterruptRequestEntryAddressRegister(IRQENTRY)FieldDescriptions

BitFieldValueDescription

31-29Reserved0Reserved

28-0IRQENTRY0-1FFFFFFFhInterruptentrytableaddressofthecurrenthighest-priorityinterruptrequest(IRQ).

ARMInterruptController(AINTC) 94SPRUEP9A–May2008

SubmitDocumentationFeedback