5.3PLL2Control

PLLDIV1(/1Prog)

PLL2_SYSCLK1

(DDR2_PHY)

1

0

PLLEN

PLL

PLLM

CLKIN/OSCIN

(A)

(A) AsselectedbythePLL2PLLCTL register

PLLOUT

www.ti.com

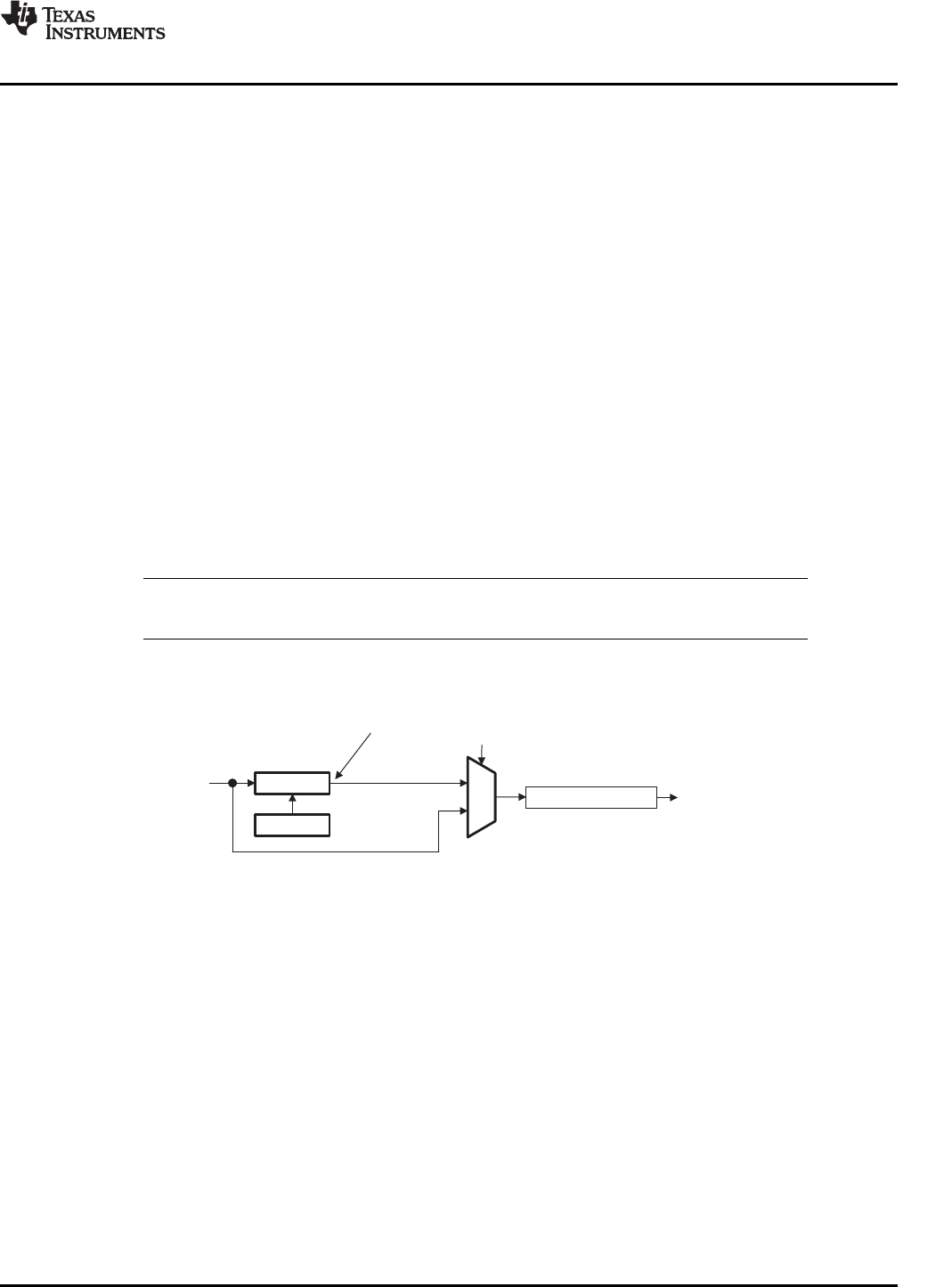

PLL2Control

PLL2providestheclockfromwhichtheDDR2memorycontrollerclockisderived.Thisisaseparateclock

systemfromthePLL1clocksprovidedtoothercomponentsofthesystem.Thisdedicatedclockallowsthe

reductionofthecoreclockratestosavepowerwhilemaintainingtherequiredminimumclockratefor

DDR2.PLL2mustbeconfiguredtooutputa2xclocktotheDDR2PHYinterface.

TheDDR2PLLcontroller(PLLC2)controlsPLL2,whichacceptstheclockfromtheoscillatorand

generatesthevariousfrequencyclocksneededfortheDDR2memorycontroller.Figure5-3showsthe

customizationofPLL2intheDM646xDMSoC.

•TheSYSCLKdividerisprogrammable.

•AUXCLKandSYSCLKBParenotused.

PLL2suppliestheDDR2memorycontrollerclock.SoftwarecontrolsPLL2operationthroughthePLLC2

registers.ThePLLMbitsinthePLLmultipliercontrolregister(PLLM)controlthePLL2multiplier.The

PLL2multipliermaybemodifiedbysoftware(forexample,totunetheDDR2memorycontrollerinterface

forbestperformance).

ThePLL2outputclockmustbedivided-downtotheDDR2memorycontrolleroperatingrange.

Atpower-up,PLL2ispowered-downandmustbepowered-upbysoftwarethroughthePLLPWRDNbitin

thePLLcontrolregister(PLLCTL).ThePLLC2isinbypassmodeandtheDDR2memorycontrollerclock

isprovideddirectlyfromtheinputreferenceclock.OncethePLLispowered-upandlocked,softwaremay

switchthedevicetoPLLmodeoperationbysettingthePLLENbitinPLLCTL.

RegistersusedinPLLC2arelistedinTable5-4.

Note:PLLDIV1defaultsto/1atresetandcanbemodifiedafterreset.PLLDIV2throughPLLDIV9

arenotsupportedonPLL2.

Figure5-3.PLL2StructureinTMS320DM646xDMSoC

SPRUEP9A–May2008PLLController41

SubmitDocumentationFeedback