8.3.4ClearingInterrupts

8.3.5EnablingandDisablingInterrupts

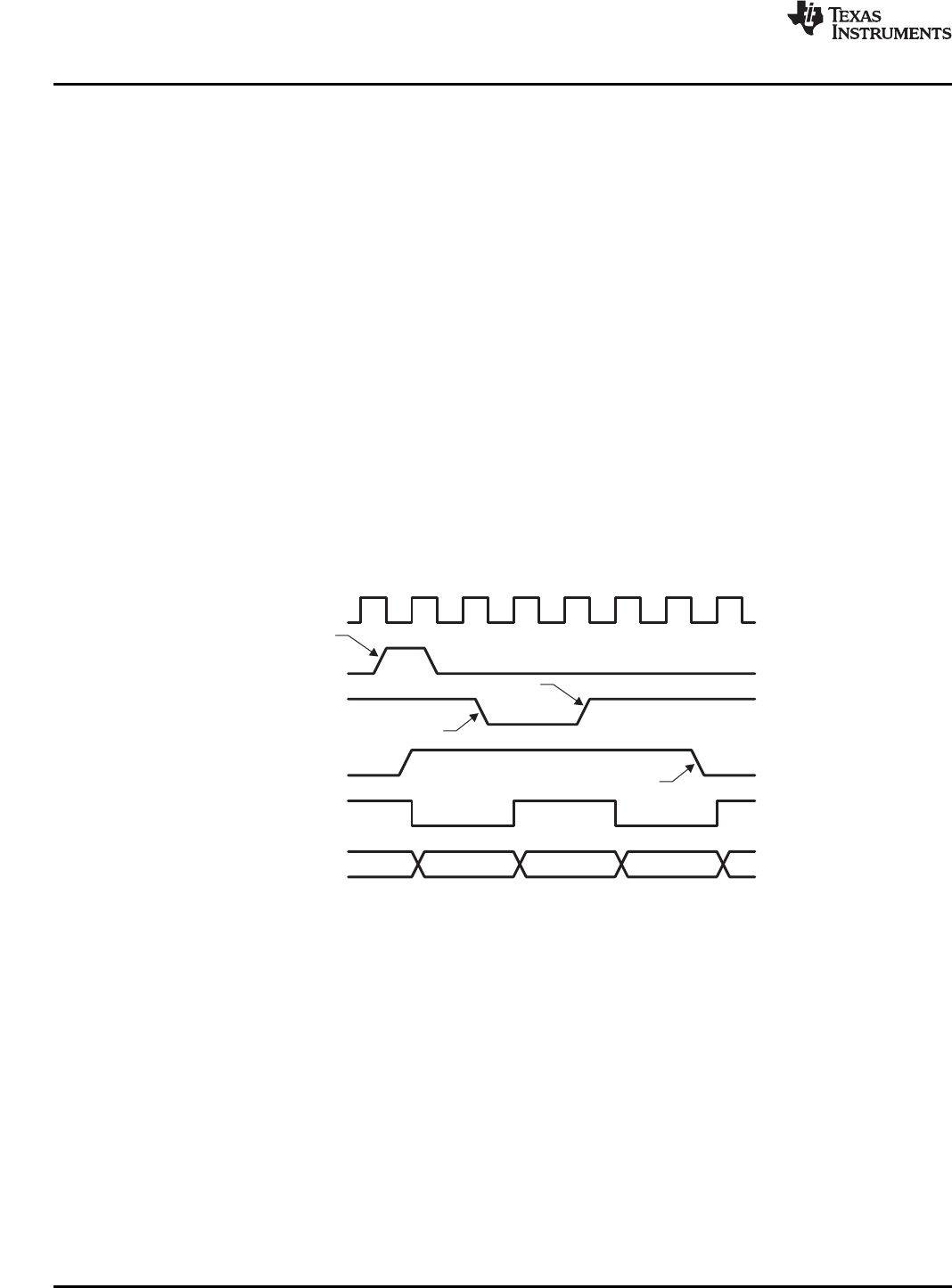

CLK

EABASE VECTORn

EABASE

VECTORn

INTn

EINTn

IRQn/FIQn

IRQz/FIQz

ENTRY

Eventpulse

Enabled

Disabled

Cleared

AINTCMethodology

www.ti.com

2.FortheIRQENTRY:

•IfIERAWis0,IRQENTRYreflectsthestateofthehighestprioritypendingenabledIRQinterrupt.If

theactiveIRQinterruptisclearedinIRQn,thenIRQENTRYisimmediatelyupdatedwiththevector

ofthenexthighestprioritypendingenabledIRQinterrupt.

•IfIERAWis1,IRQENTRYreflectsthestateofthehighestprioritypendingIRQinterrupt(enabled

ornot).IftheactiveIRQinterruptisclearedinIRQn,thenIRQENTRYisimmediatelyupdatedwith

thevectorofthenexthighestprioritypendingIRQinterrupt(pendingornot).

EventscausetheirmatchingbitintheFIQorIRQregister(dependingontheeventpriority)tobecleared

to0.Aneventisclearedbywritinga1tothecorrespondingbitintheFIQorIRQregister.Writinga1to

thecorrespondingbitsetsthebitbacktoa1.Writinga0toaneventbitdoesnotaffectitsvalue.

TheAINTChastwomethodsforenablinganddisablinginterrupts:immediateordelayed,basedonthe

settingoftheIDMODEbitintheINTCTLregister.When0(default),clearinganinterrupt'sEINTbithasan

immediateeffect.Theprioritizerremovesthedisabledinterruptfromconsiderationandadjuststhe

IRQ/FIQENTRYvaluecorrespondingly.Ifnootherinterruptsarepending,thentheIRQz/FIQzoutputto

theARMmayalsogoinactive.Enablingtheinterruptifitisalreadypendingtakesimmediateaffect.Thisis

showninFigure8-3.

Figure8-3.ImmediateInterruptDisable/Enable

IfIDMODEis1,thentheEINTeffectisdelayed.Essentially,theactiveinterruptstatusislatcheduntil

clearedbytheARM.IfEINTiscleared,theprioritizercontinuestousetheinterruptandtheIRQz/FIQz

remainsactive.OncetheARMclearsthependinginterrupt,furtherinterruptsaredisabled.Inthesame

way,settingEINTdoesnotcausethepreviouslypendinginterrupteventtobecomeenableduntilithas

beenclearedfirst.ThedisableoperationisshowninFigure8-4.

ARMInterruptController(AINTC) 90SPRUEP9A–May2008

SubmitDocumentationFeedback