5.4.5PLLControllerDivider1Register(PLLDIV1)

www.ti.com

PLLControllerRegisterMap

ThePLLcontrollerdivider1register(PLLDIV1)isshowninFigure5-8anddescribedinTable5-9.

Divider1controlsthedividerforSYSCLK1.

Note:OntheDM646xDMSoC,allPLL1SYSCLKndividersareprogrammablebutyoushouldnot

changethedividervaluetomaintaintheclockratiosbetweenvariousmodulesofthedevice.

Youshouldonlyusethepower-updefaultdividervaluesforallPLL1SYSCLKndividersfor

normaldeviceoperation.

PLL2SYSCLK1dividervalueisprogrammableandyoumaychangethedividervalueforthe

desiredDDR2memorycontrollerclockfrequency.

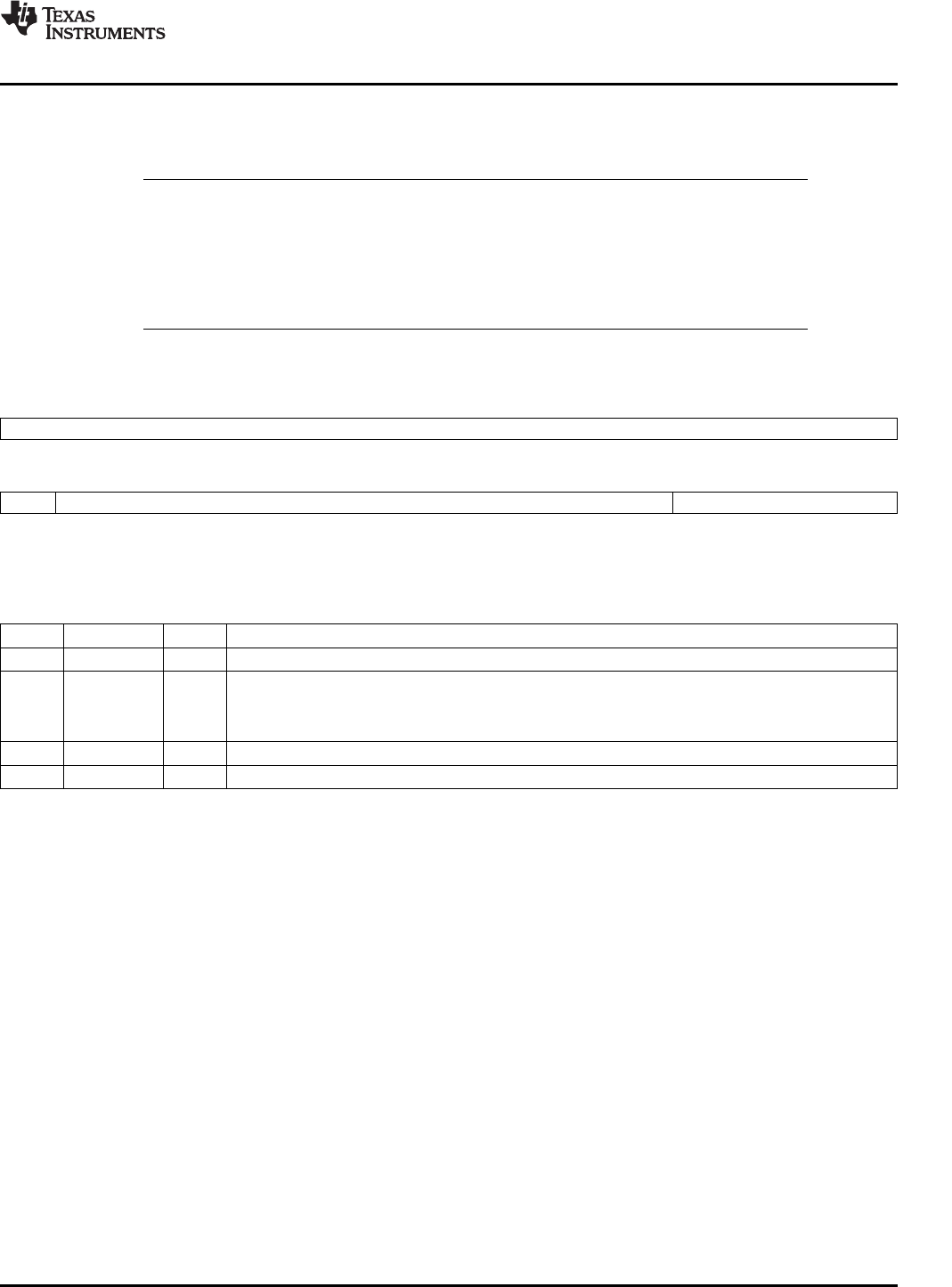

Figure5-8.PLLControllerDivider1Register(PLLDIV1)

3116

Reserved

R-0

1514430

D1ENReservedRATIO

R/W-0R-0R/W-0

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Table5-9.PLLControllerDivider1Register(PLLDIV1)FieldDescriptions

BitFieldValueDescription

31-16Reserved0Reserved

15D1ENDividerenableforSYSCLK1.

0Disable

1Enable

14-4Reserved0Reserved

3-0RATIO0-FhDividerratio.DividerValue=RATIO+1.RATIOdefaultsto0(PLLdivideby1).

SPRUEP9A–May2008PLLController49

SubmitDocumentationFeedback