8.4.3InterruptRequestStatusRegister0(IRQ0)

8.4.4InterruptRequestStatusRegister1(IRQ1)

www.ti.com

AINTCRegisters

Theinterruptrequeststatusregister0(IRQ0)isshowninFigure8-7anddescribedinTable8-5.Interrupt

statusofINT[31:0](ifmappedtoIRQ).

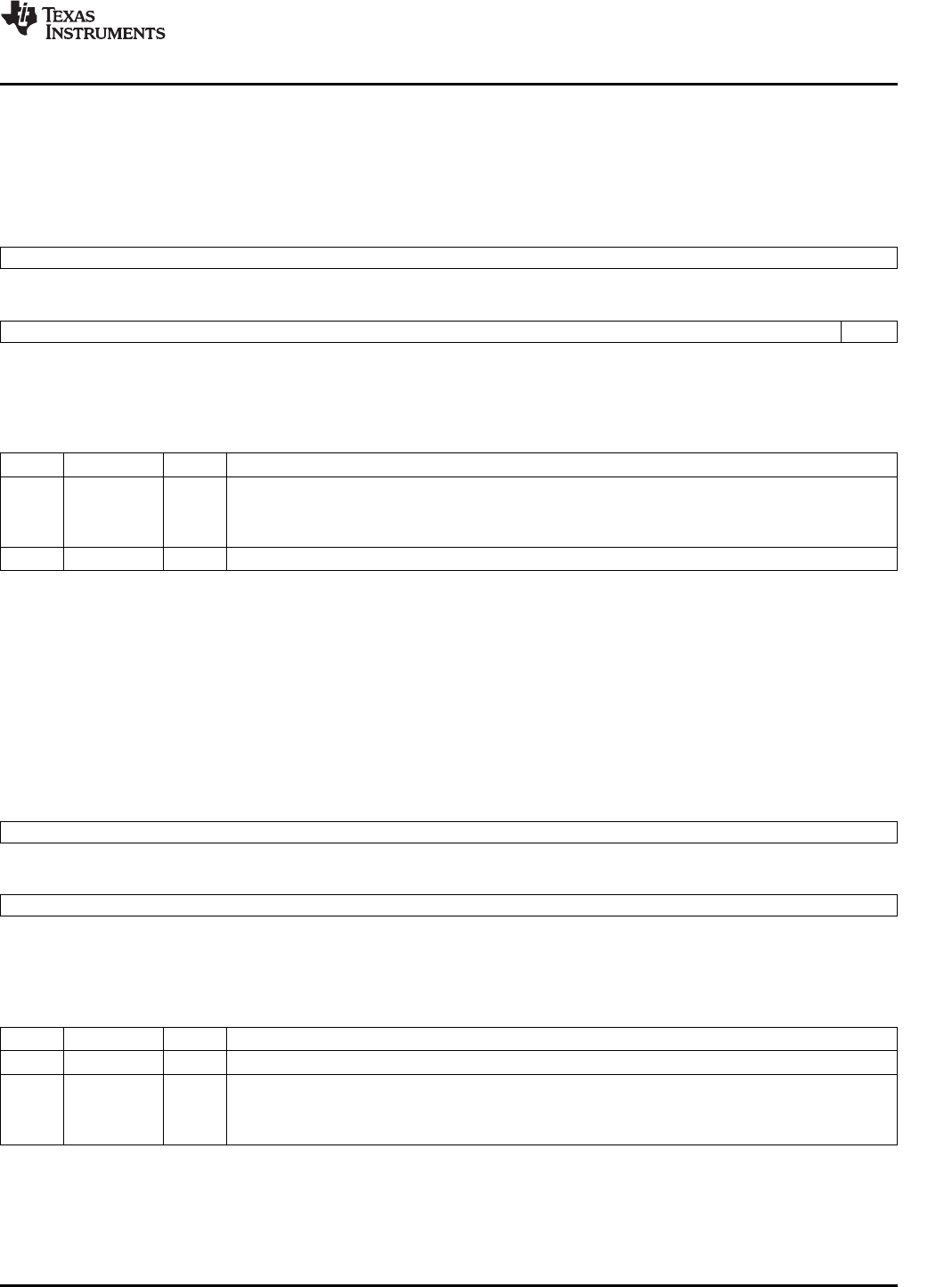

Figure8-7.InterruptRequestStatusRegister0(IRQ0)

3116

IRQ

R/W-1

1510

IRQIRQ0

R/W-1R-1

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Table8-5.InterruptRequestStatusRegister0(IRQ0)FieldDescriptions

BitFieldValueDescription

31-1IRQ[n]InterruptstatusofINTn,ifmappedtointerruptrequest(IRQ31-1).

0Whenreadingbit,interruptoccurred.

1Whenwritingbit,acknowledgeinterrupt.

0IRQ01Interrupt0isalwaysmappedtofastinterruptrequest(FIQ).

Theinterruptrequeststatusregister1(IRQ1)isshowninFigure8-8anddescribedinTable8-6.Interrupt

statusofINT[63:32](ifmappedtoIRQ).

Figure8-8.InterruptRequestStatusRegister1(IRQ1)

3116

Reserved

R-1

150

IRQ

R/W-1

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Table8-6.InterruptRequestStatusRegister1(IRQ1)FieldDescriptions

BitFieldValueDescription

31-16Reserved1Reserved

15-0IRQ[n]InterruptstatusofINTn,ifmappedtofastinterruptrequest(IRQ47-32).

0Whenreadingbit,interruptoccurred.

1Whenwritingbit,acknowledgeinterrupt.

SPRUEP9A–May2008ARMInterruptController(AINTC)93

SubmitDocumentationFeedback