8.3AINTCMethodology

IRQ/FIQ

map

00

0-63

INTn

INTPRIn[2:1]

IRQn

INT

enable

FIQn

EINTn

Prioritizer

IRQn

EABASE

IRQzTo ARM Entry

address

generator

IRQENTRY

Entry

address

generator

FIQENTRY

Prioritizer

FIQn

FIQz To ARM

8.3.1InterruptMapping

AINTCMethodology

www.ti.com

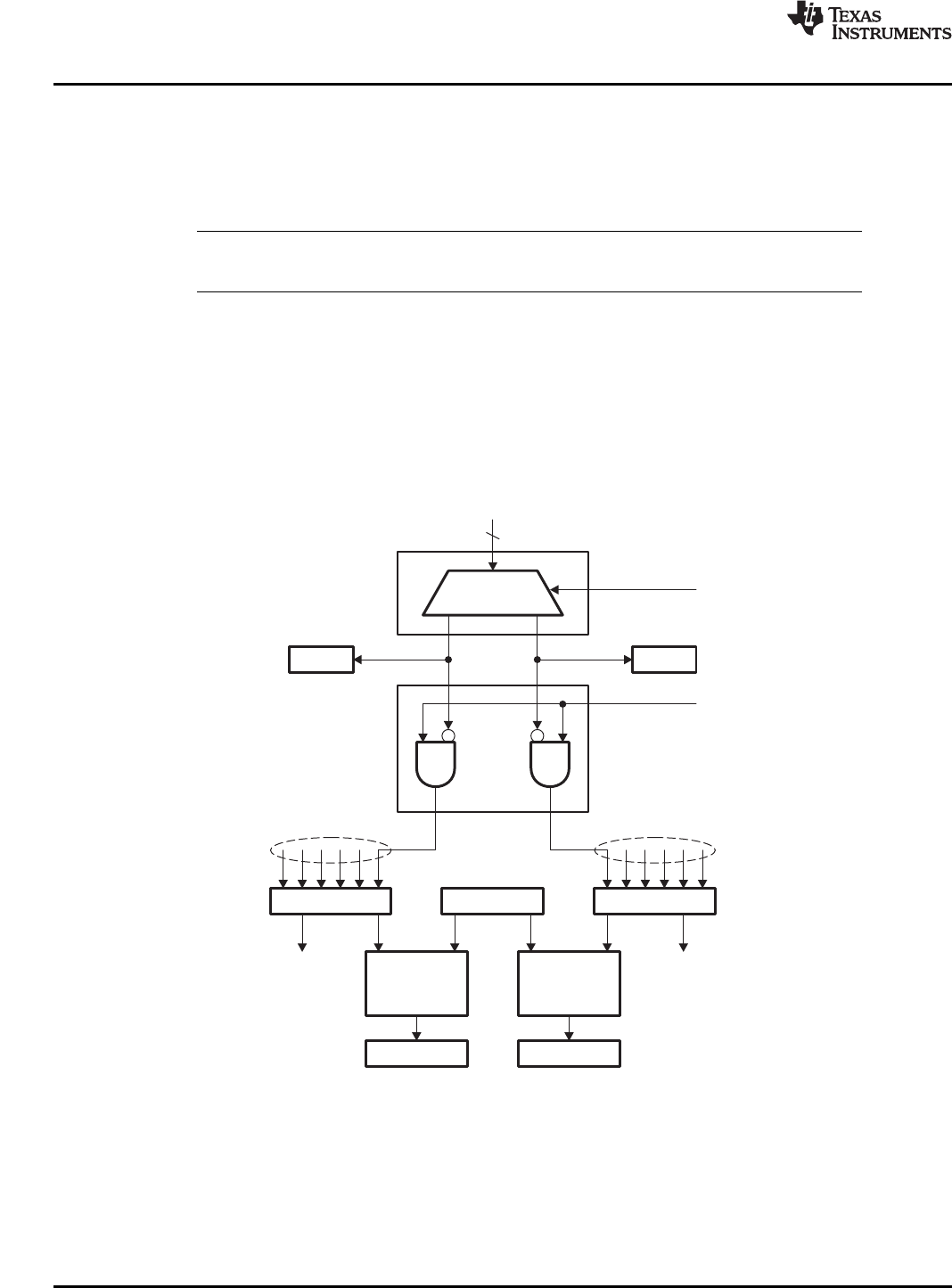

AINTCmethodologyisillustratedinFigure8-1anddescribedbelow.

•Whenaninterruptoccurs,thestatusisreflectedineithertheFIQnortheIRQnregisters,depending

upontheinterrupttypeselected.

•Interruptsareenabledordisabled(masked)bysettingtheEINTnregister.

Note:Evenifaninterruptismasked,thestatusinterruptisstillreflectedintheFIQnandtheIRQn

registers.

•Whenaninterruptfromanyinterruptchanneloccurs(forwhichinterruptisenabled),anIRQorFIQ

interruptgeneratestotheARM926EJcore(dependingonwhethertheinterruptchannelismappedto

IRQorFIQinterrupt).TheARMthenbranchestotheIRQorFIQinterruptroutine.

•TheAINTCgeneratestheentryaddressofthependinginterruptwiththehighestpriorityandstoresthe

entryaddressintheFIQENTRYortheIRQENTRYregister,dependingonwhethertheinterruptis

mappedtoIRQorFIQinterrupt.TheIRQorFIQISRcanthenreadtheentryaddressanditsbranchto

theISRoftheinterrupt.

Figure8-1.AINTCFunctionalDiagram

EacheventinputismappedtoeithertheARMIRQortotheFIQinterruptbasedontheprioritylevel

selectedintheINTPRInregister.Eventswithapriorityof0or1aredesignatedasFIQs;eventswith

prioritiesof2-7aredesignatedasIRQs.TheappropriateIRQ/FIQregisterscaptureinterruptevents.

EacheventcausesanIRQorFIQtogenerateonlyifthecorrespondingEINTbitenablesit.TheEINTbit

enablesordisablestheeventregardlessofwhetheritismappedtoIRQortoFIQ.TheIRQ/FIQregister

alwayscaptureseachevent,regardlessofwhethertheinterruptisactuallyenabled.

88ARMInterruptController(AINTC)SPRUEP9A–May2008

SubmitDocumentationFeedback