96 SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

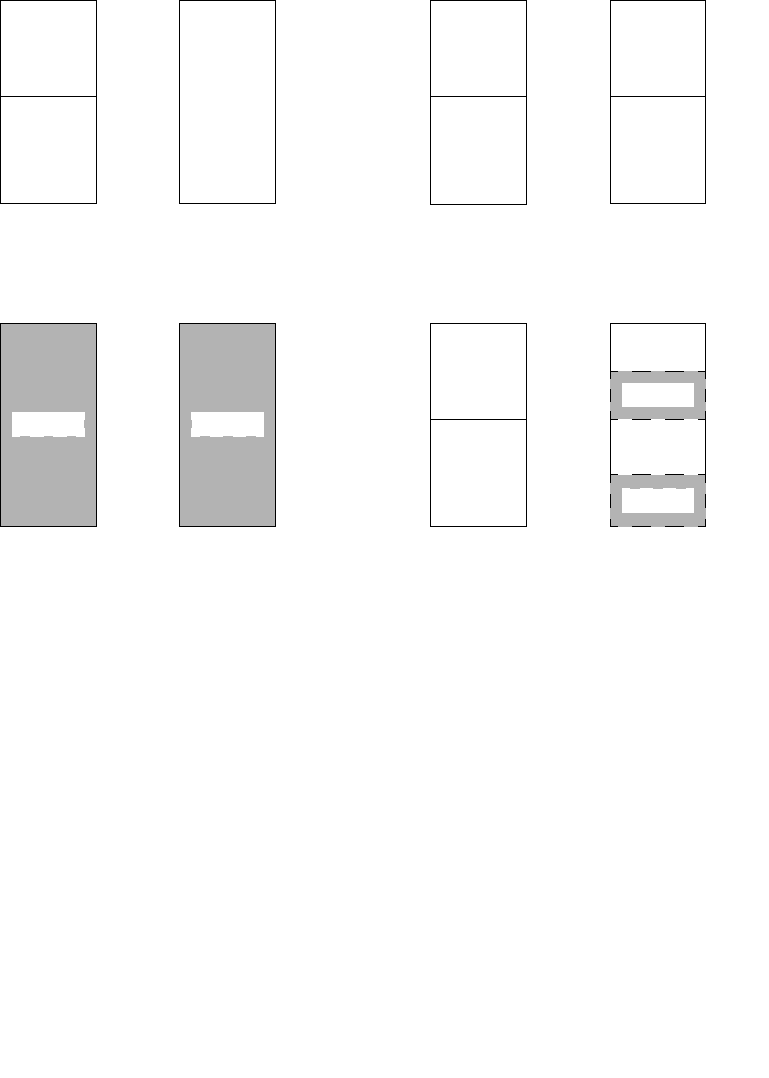

FIGURE F-2

Index number of set associative TLBs

I/D MMU TLB Tag Access Register

On an ASI store to the TLB Data Access or Data In Register, SPARC64 V verifies the

consistency between the Tag Access Register and the data to be written. If their

indexes are inconsistent, the TLB entry is not updated. However, SPARC64 V does

not verify the consistency if TTE.V = 0 for the TTE to be written. This enables

demapping of specified TLB entries through the TLB Data Access Register. Software

can use this feature to validate faulty TLB entries.

On verifing the consistency, the bits position and length that is interpreted as index

against the data in Tag Access Register varies on the page size and MCNTL.RMD. In 8-

Kbyte page, bits[21:13] is conscidered as index and compared with the index field of

TLB Data Access or Data In Register. In 4-Mbyte page, bits[30:22] when

MCNTL.RMD=10, or bits[29:22] when MCNTL.RMD=11, is conscidered as index.

0

8-Kbyte page entry

way0

way1

511

512

1023

RMD=00

2047

1024

0

8-Kbyte page entry

way0

way1

511

512

1023

RMD=10

2047

1024

0

1023

RMD=01

2047

1024

0

8-Kbyte page entry

way0

way1

511

512

1023

RMD=11

2047

1024

reserved reserved

4-Mbyte page entry

4-Mbyte page entry

way0

way1

way0

way1

1535

1536

1280

1535

1536

1791

1792

1279

reserved

reserved