102 SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

TABLE F-9

defines the encoding of the

FT

<6:0> field.

Data CT<1:0> R/W Context type. Saves the context attribute for the reference that invokes an

exception. For nontranslating ASI or invalid ASI, DSFSR.CT =11

02

.

00

02

:Primary

01

02

:Secondary

10

02

:Nucleus

11

02

: Reserved

When a

data_access_exception

trap is caused by an invalid combination of

an ASI and an opcode (e.g., atomic load quad, block load/store, block

commit store, partial store, or short floating-point load/store instructions),

the recording of the

DSFSR.CT

field is based on the encoding of the ASI

specified by the instruction.

Data <3> PR R/W Privileged. Indicates the CPU privilege status during the operand reference

that generates the exception. This field is valid when

DSFSR.FV

=1.

Data <2> W R/W Write. W = 1 if the reference is for an operand write operation (a store or

atomic load/store instruction).

Data <1> OW R/W Overwritten. Set when

DSFSR.FV

= 1 upon detection of a exception. This

means that the fault valid bit is not yet cleared when another fault is

detected.

Data <0> FV R/W Fault valid. Set when the DMMU detects an exception. The bit is not set on

an DMMU miss. When the FV bit is not set, the values of the remaining

fields in the

DSFSR

and

DSFAR

are undefined, except for a DMMU miss.

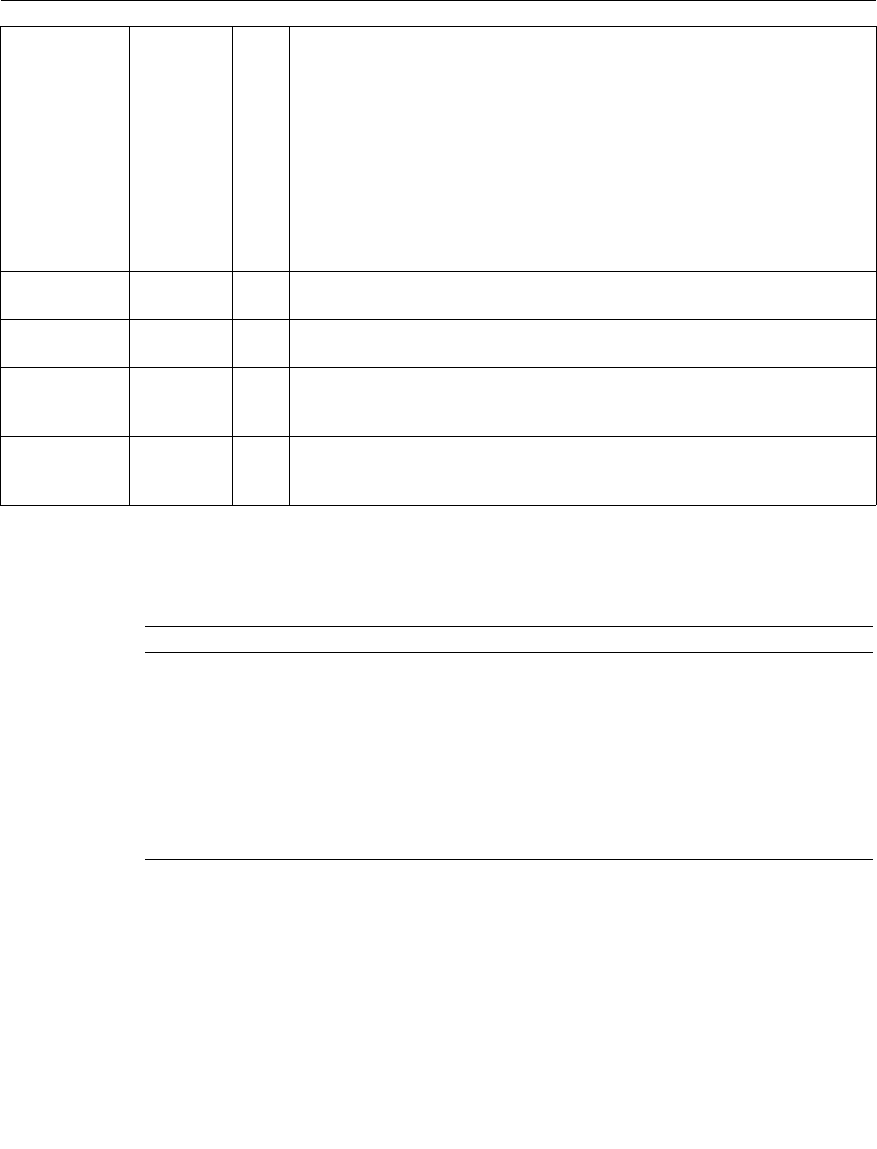

TABLE F-9

MMU Synchronous Fault Status Register FT (Fault Type) Field

FT<6:0> Error Description

01

16

Privilege violation. An attempt was made to access a privileged page

(

TTE.P

= 1) under nonprivileged mode (

PSTATE.PRIV

=0) or through a

*_AS_IF_USER ASI

. This exception has priority over a

fast_data_access_protection

exception.

02

16

Nonfaulting load instruction to page marked with the E bit. This bit is zero for

internal ASI accesses.

04

16

An attempt was made to access a noncacheable page or an internal ASI by an

atomic instruction (CASA, CASXA, SWAP, SWAPA, LDSTUB, LDSTUBA) or an

atomic quad load instruction (LDDA with ASI = 024

16

, 02C

16

, 034

16

, or 03C

16

).

TABLE F-8

D-SFSR Bit Description (3 of 3)

Bits Field Name RW Description