Release 1.0, 1 July 2002 F. Chapter A Instruction Definitions: SPARC64 V Extensions 55

■

TTE.NFO= 0

■

TTE.CP = 1

■

TTE.CV = 0

■

TTE.E = 0

■

TTE.P = 1

■

TTE.W = 0

Note –

TTE.IE depends on the endianness of the ASI. When the ASI is 034

16

,

TTE.IE =0; TTE.IE = 1 when the ASI is 03C

16

.

Therefore, the atomic quad load physical instruction can only be applied to a

cacheable memory area. Semantically, ASI_QUAD_LDD_PHYS{_L} (034

16

and

03C

16

) is a combination of ASI_NUCLEUS_QUAD_LDD and ASI_PHYS_USE_EC.

With respect to little endian memory, a Load Quadword Atomic instruction behaves

as if it comprises two 64-bit loads, each of which is byte-swapped independently

before being written into its respective destination register.

Exceptions: privileged_action

PA_watchpoint

(recognized on only the first 8 bytes of a transfer)

illegal_instruction

(misaligned rd)

mem_address_not_aligned

data_access_exception

data_access_error

fast_data_access_MMU_miss

fast_data_access_protection

A.35 Memory Barrier

Format (3)

Assembly Language Syntax

membar membar_mask

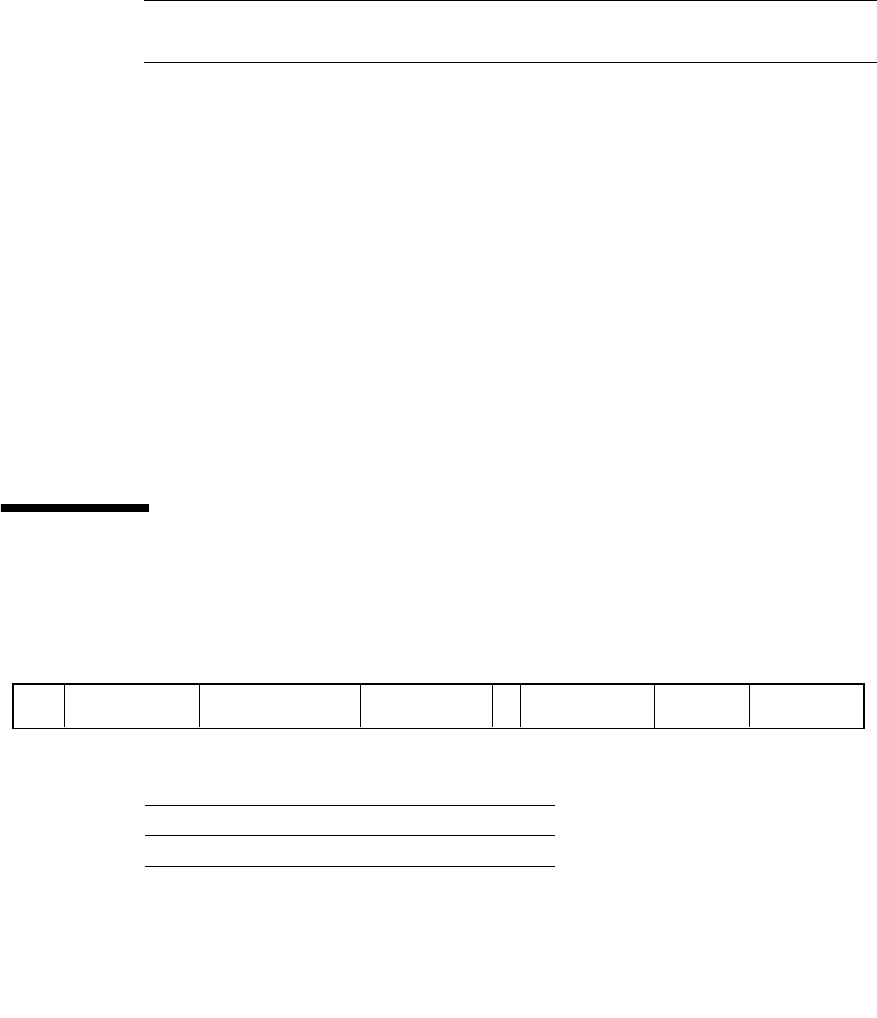

31 141924 18 13 12 02530 29

10 0 op3 0 1111

i=1

—

43

mmask

6

7

cmask