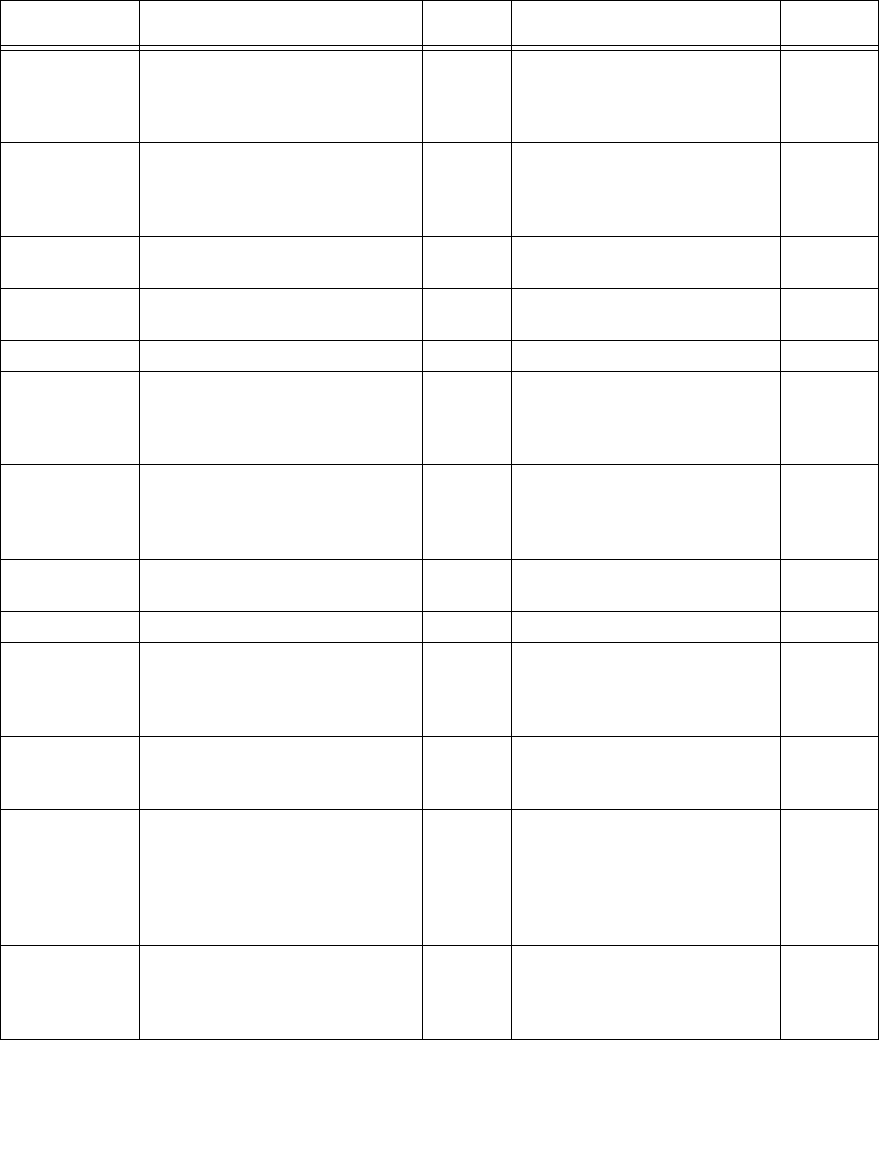

Release 1.0, 1 July 2002 F. Chapter S Summary of Differences between SPARC64 V and UltraSPARC-III 221

Error status ASI 4C

16

/08

16

(ASI_UGESR):

SPARC64V implements an error

status register to indicate where an

error was detected.

165 Not implemented. —

Error Control

Register

ASI 4C

16

/10

16

(ASI_ECR):

SPARC64 V implements a control

register to signal/suppress a trap

when an error was detected.

161 Not implemented. —

ASI_AFAR Multiple registers (VA addressed)

for L1D, L2. 43-bit PA.

177 Single register, multiple use.

43-bit PA.

P. 4.2

ASI device and

serial ID

ASI 53

16

: provides an identification

code for each processor.

119 ASI 53

16

: ASI_SERIAL_ID ?

I/D SFSR Many differences. 97 Many differences. Chapter 8

Error

Identification

Register (EIDR)

ASI 6E

16

: SPARC64 V implements

an error ID register. Used to encode

CPU-ID into error marking when

an unrecoverable ECC error occurs.

161 Not implemented. —

I-cache and

Branch

Prediction Array

Not supported. — ASIs 66

16

through 68

16

and ASI

6F

16

support instruction cache

and branch prediction array

diagnostic access.

V.4, V.5

MCU Control

Register

SPARC64 V does not have an

MCU.

— ASI 72

16

: MCU Control Register. App. U

Module ID bits Implements 5-bit IDs. 136 Implements 10-bit IDs. R.2

Performance

counters

SPARC64 V implements a different

set of performance counters than

those of UltraSPARC-III.

203 UltraSPARC-III implements a

different set of performance

counters than those of

SPARC64 V.

App. Q

Dispatch

Control Register

(DCR)

SPARC64 V does not have the DCR. 22 UltraSPARC-III defines the DCR.5.2.11

Version Register

(VER)

For SPARC64 V:

manuf = 0004

16

,

impl = 5,

mask = <mask revision number>,

maxtl = 5,

maxwin = 7.

20 For UltraSPARC-III:

manuf = 0017

16

,

impl = 0014

16

,

mask = <mask revision number>,

maxtl = 5,

maxwin = 7.

C.3.4

Watchdog reset

trap

Supports

watchdog_reset

trap. By

setting OPSR,

watchdog_reset

trap

is not signalled and CPU stays in

error_state.

140 Supports

watchdog_reset

trap. O.1

TABLE T-1

SPARC64 V and UltraSPARC-III Differences

(3 of 3)

Feature SPARC64 V

SPARC64 V

Page UltraSPARC-III

UltraSPARC-

III Section