52 SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

detects any conditions for an

unfinished_FPop

trap, the Floating-point Multiply-Add/

Subtract instruction generates the

unfinished_FPop

exception. In this case, none of rd,

cexc, or aexc are modified.

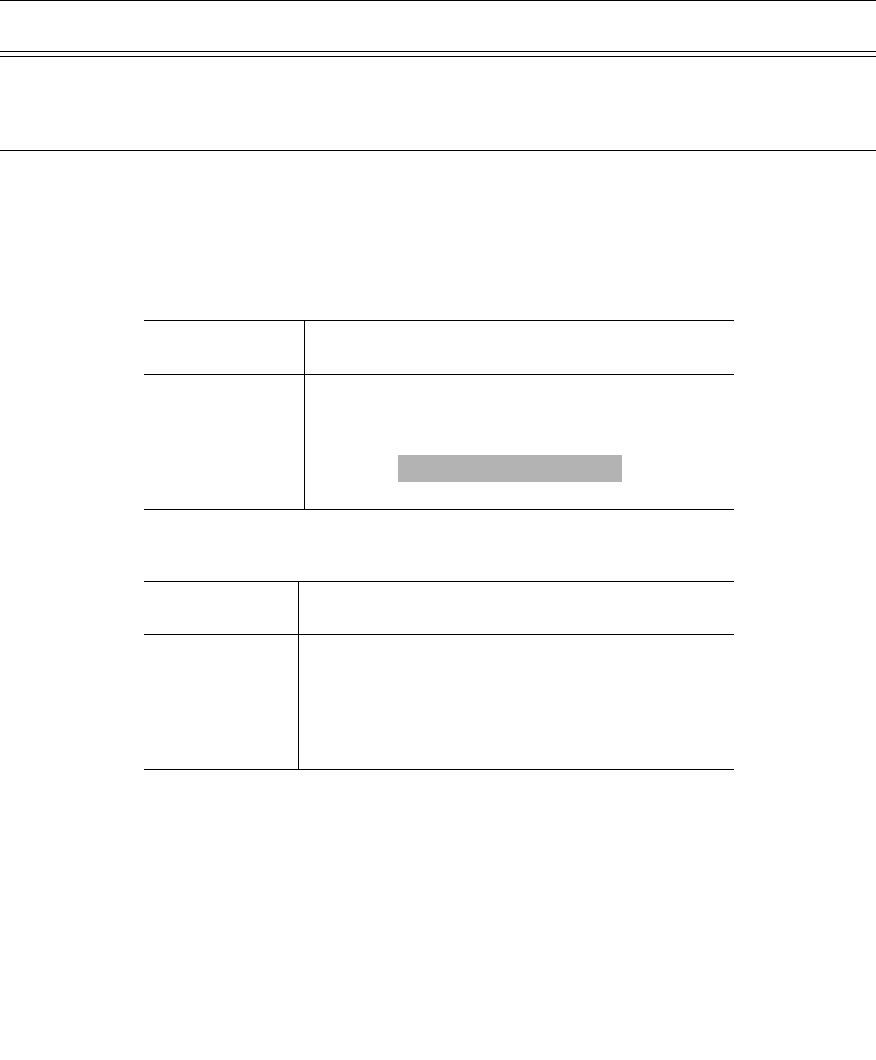

Detailed contents of cexc and aexc depending on the various conditions are

described in

TABLE A-3

and

TABLE A-4

. The following terminology is used: uf, of, inv,

and nx are nontrapping IEEE exception conditions—underflow, overflow, invalid

operation, and inexact, respectively.

In the tables, the conditions in the shaded columns are all reported as an

unfinished_FPop

trap by SPARC64 V. In addition, the conditions with “

—

” do not

exist.

TABLE A-2

Exceptions in Floating-Point Multiply-Add/Subtract Instructions

FMUL

IEEE754 trap No trap No trap

FADD/SUB

— IEEE754 trap No trap

cexc

Exception condition of FMUL Exception condition of FADD Logical or of the nontrapping exception

conditions of FMUL and FADD/SUB

aexc

No change No change Logical OR of the cexc (above) and the

aexc

TABLE A-3

Non-Trapping cexc When

FSR.NS

=0

FADD

none nx of nx inv

FMUL

none none nx of nx inv

nx nx nx of nx inv nx

of nx of nx of nx of nx inv of nx

uf nx uf nx

uf nx uf of nx uf inv nx

inv inv ——inv

TABLE A-4

Non-Trapping aexc When

FSR.NS

=1

FADD

none nx of nx uf nx inv

FMUL

none none nx of nx uf nx inv

nx nx nx of nx uf nx inv nx

of nx of nx of nx of nx — inv of nx

uf nx uf nx —— — uf inv nx

inv inv —— — inv