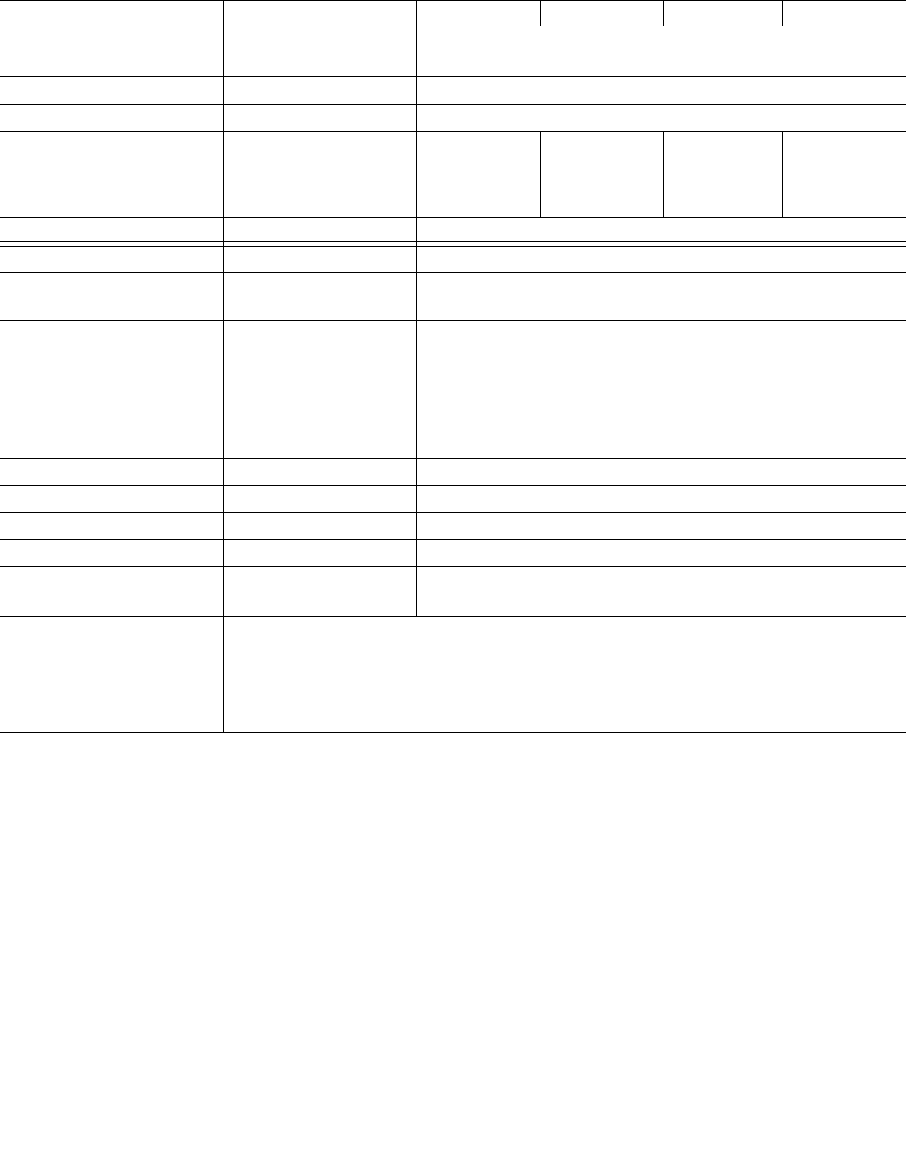

142 SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

TLE

CLE

0/ Copied from

CLE

0/ Unchanged

Copied from

CLE

Unchanged

TBA

<63:15>

Unknown/Unchanged

Unchanged

PIL

Unknown/Unchanged Unchanged

CWP

Unknown/Unchanged Unchanged

except for

register win-

dow traps

Unchanged Unchanged Unchanged

except for

register win-

dow traps

FPRS

Unknown/Unchanged Unchanged

TL MAXTL

min

(

TL

+ 1,

MAXTL

)

TPC[TL]

TNPC[TL]

Unknown/Unchanged

Unknown/Unchanged

PC

nPC

TSTATE

CCR

ASI

PSTATE

CWP

PC

nPC

Unknown/Unchanged

CCR

ASI

PSTATE

CWP

PC

nPC

CANSAVE

Unknown/Unchanged Unchanged

CANRESTORE

Unknown/Unchanged Unchanged

OTHERWIN

Unknown/Unchanged Unchanged

CLEARWIN

Unknown/Unchanged Unchanged

WSTATE

OTHER

NORMAL

Unknown/Unchanged

Unknown/Unchanged

Unchanged

Unchanged

VER MANUF

IMPL

MASK

MAXTL

MAXWIN

0004

16

5

16

Mask dependent

5

16

7

16

1.Hard POR occurs when power is cycled. Values are unknown following hard POR. Soft POR occurs when

UPA_RESET_L is asserted. Values are unchanged following soft POR.

2.The first watchdog timeout trap is taken in execute_state (i.e. PSTATE.RED = 0), subsequent watchdog timeout traps

as well as watchdog traps due to a trap @ TL = MAX_TL are taken in RED_state. See Section O.1.2, Watchdog Reset

(WDR), on page 138 for more details.

TABLE O-1

Nonprivileged and Privileged Register State after Reset and in

RED_state

(Continued)

Name POR

1

WDR

2

XIR SIR

RED_state