F.APPENDIX

219

S

Summary of Differences between

SPARC64 V and UltraSPARC-III

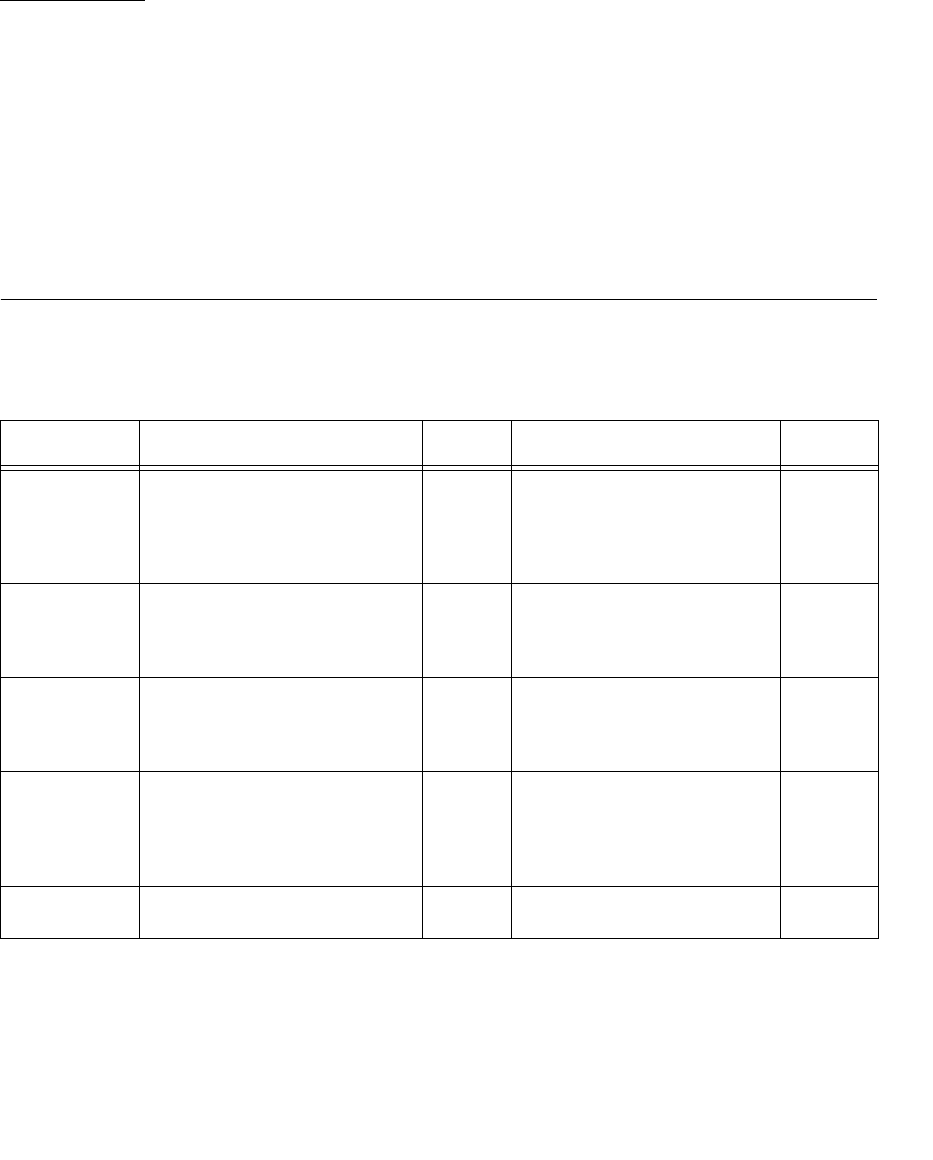

The following table summarizes differences between SPARC64 V and UltraSPARC-III

ISAs. This list is a summary, not an exhaustive list.

TABLE T-1

SPARC64 V and UltraSPARC-III Differences

(1 of 3)

Feature SPARC64 V

SPARC64 V

Page UltraSPARC-III

UltraSPARC-

III Section

MMU

architecture

SPARC64 V supports an

UltraSPARC II-based MMU model.

TLBs are split between instruction

and data. Each side has a 2-level

TLB hierarchy.

85 UltraSPARC-III implements a flat

extended version of UltraSPARC

II’s MMU architecture.

F-1

TTE format SPARC64 V supports a 43-bit

physical address. In addition, the

CV bit is ignored and unaliasing is

maintained by hardware.

86 UltraSPARC-III supports a 43-bit

physical address. Millennium

will support a 47-bit PA.

F-2

TLB locking

mechanism

Lock entries are supported in both

fully-associative ITLB (fITLB) and

fully-associative DTLB (fDTLB), 32-

entry each.

86 Lock entries supported only in

the 16-entry fully-associative

TLBs.

F-1, F-2

TSB hashing

algorithm

Direct hashing with contents of the

Context-ID register (13-bit). Has a

UltraSPARC I/II compatibility

mode.

88 Hash field in pointer extension is

used for hashing address. Setting

0 in the field maintains

compatibility with UltraSPARC

I/II.

F. 10.7

Floating-point

Multiply-ADD

SPARC64 V implements these

instructions in IMPDEP2.

50 Does not support FMA

instructions.

—