128 SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

M.2 Cache Coherency Protocols

The CPU uses the UPA MOESI cache-coherence protocol; these letters are acronyms

for cache line states as follows:

A subset of the MOESI protocol is used in the on-chip caches as well as the D-Tags in

the system controller.

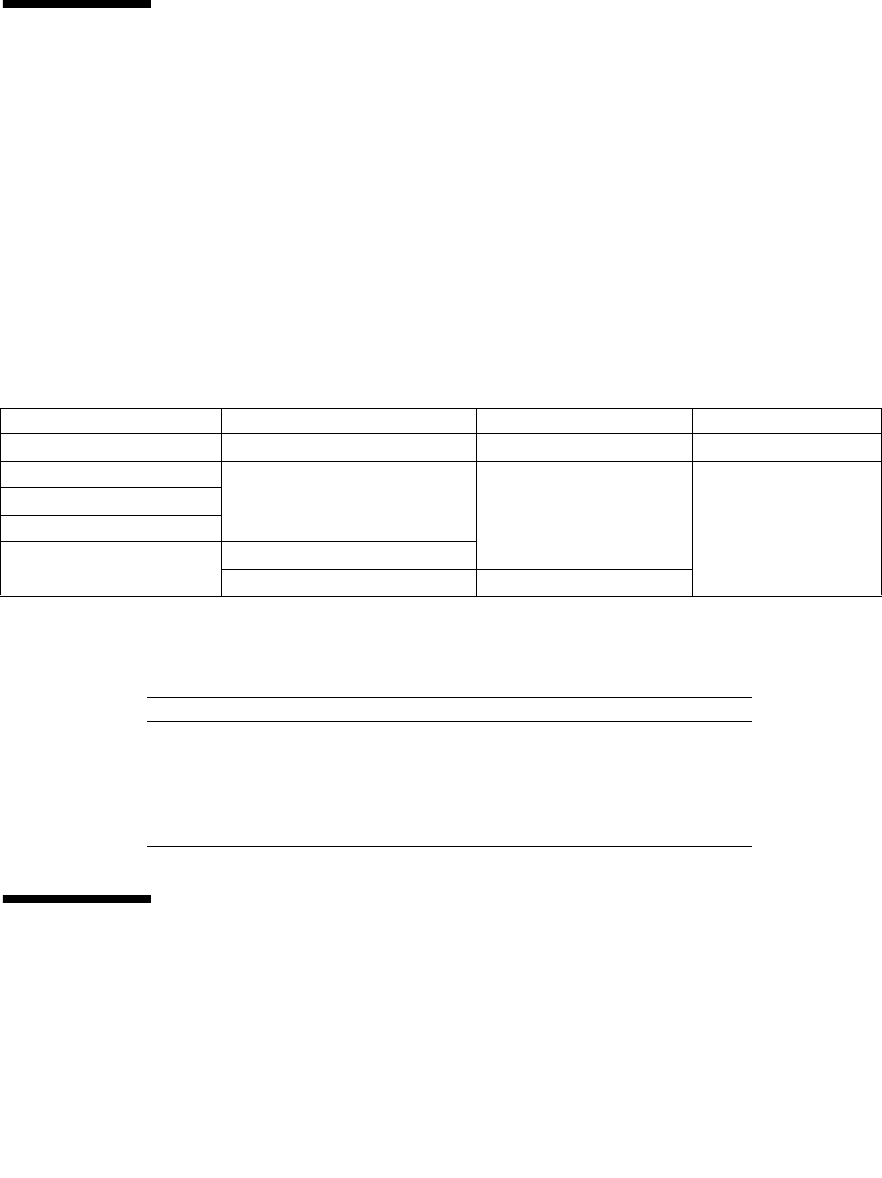

TABLE M-4

shows the relationships between the protocols.

TABLE M-5

shows the encoding of the MOESI states in the L2 Cache.

M.3 Cache Control/Status Instructions

Several ASI instructions are defined to manipulate the caches. The following

conventions are common to all of the load and store alternate instructions defined in

this section:

MExclusive modified

O Shared modified (owned)

EExclusive clean

SShared clean

I Invalid

TABLE M-4

Relationships Between Cache Coherency Protocols

L2-Cache L1D-Cache SAT (store ownership) L1I-Cache

Invalid (I) Invalid (I) Invalid (I) Invalid (I)

Shared Clean (S)

Invalid (I) or Clean (C)

Invalid (I)

Invalid (I) or

Valid (V)

Shared Modified (O)

Exclusive Clean (E)

Exclusive Modified (M)

Invalid (I)

Exclusive Modified (M) Valid (V)

TABLE M-5

L2 Cache MOESI States

Bit 2 (Valid) Bit 1 (Exclusive) Bit 0 (Modified) State

0 ——Invalid (I)

100Shared clean (S)

110Exclusive clean (E)

1 0 1 Shared modified (O)

111Exclusive modified (M)