66 SPARC JPS1 Implementation Supplement: Fujitsu SPARC64 V • Release 1.0, 1 July 2002

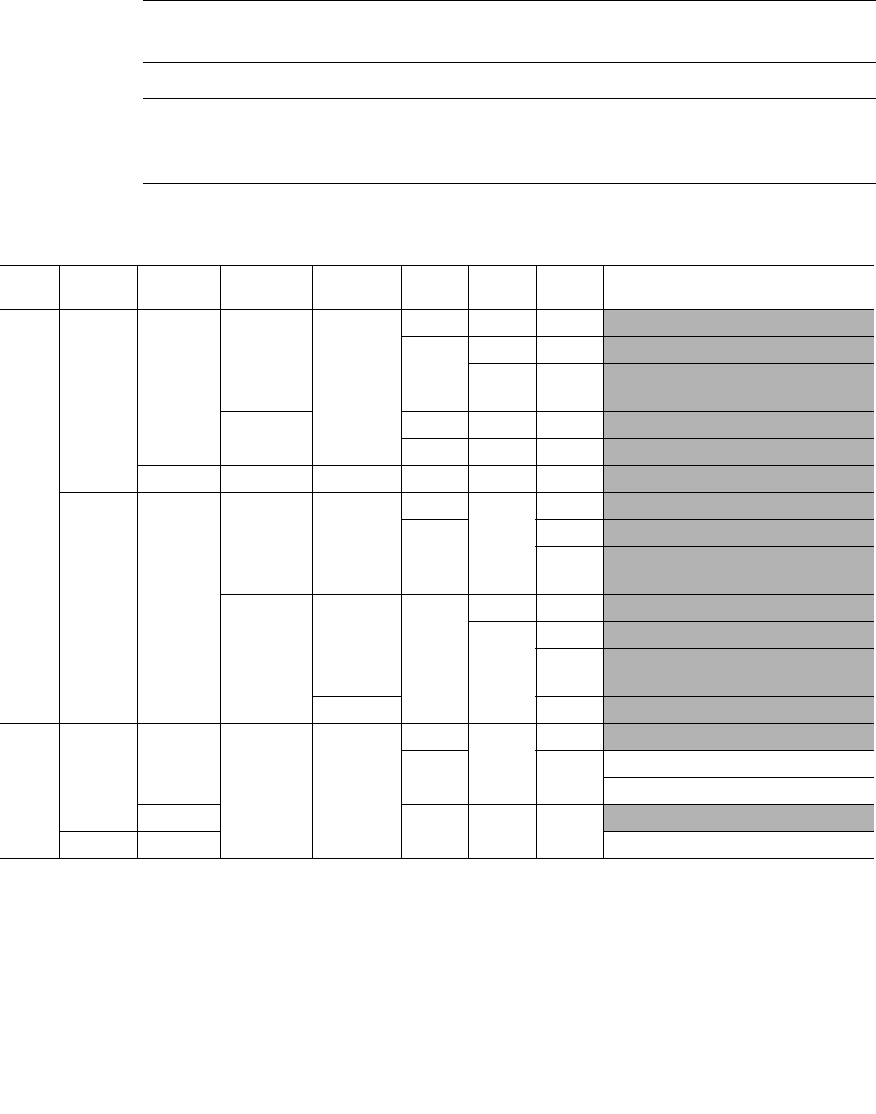

summarizes the behavior of SPARC64 V floating-point hardware depending on

FSR.NS.

Note –

The result and behavior of SPARC64 V of the shaded column in the tables

Table B-5 and Table B-6 conform to IEEE754-1985 standard.

Note –

Throughout Table B-5 and Table B-6, lowercase exception conditions such as

nx, uf, of, dv and nv are nontrapping IEEE 754 exceptions. Uppercase exception

conditions such as NX, UF, OF, DZ and NV are trapping IEEE 754 exceptions.

TABLE B-5

Floating-Point Exceptional Conditions and Results

FSR.N

S

Denorm :

Norm

1

1. One of the operands is a denormalized number, and the other operand is a normal or a denormalized number

(non- zero, non-NaN, and non-infinity).

Result

Denorm

2

2. The result before rounding turns out to be a denormalized number.

Pessimistic

Zero

Pessimistic

Overflow UFM OFM NXM Result

0

No Yes

Yes

—

1 ——

UF

0 — 1 NX

— 0

uf + nx, a signed zero, or a signed

Dmin

3

3. Dmin = denormalized minimum.

No 1 ——UF

0 ——

unfinished_FPop

4

4. If the FPop is either

FADD

{

s,d

}, or

FSUB

{

s,d

} and the operation is 0 ± denormalized number, SPARC64 V does

not generate an unfinished_FPop and generates a result according to IEEE754-1985 standard.

No —————Conforms to IEEE754-1985

Yes n/ a

Yes —

1

—

— UF

01

NX

0 uf + nx, a signed zero, or a signed

Dmin

No Yes —

1 —

OF

01

NX

0

of + nx, a signed infinity, or a

signed Nmax

5

5. Nmax = normalized maximum.

No ——

unfinished_FPop

1

No Yes

——

1 ——

UF

0 — 1NX

0 uf + nx, a signed zero

No ———

Conforms to IEEE754-1985

Yes — TABLE B-6