Release 1.0, 1 July 2002 F. Chapter 1 Overview 5

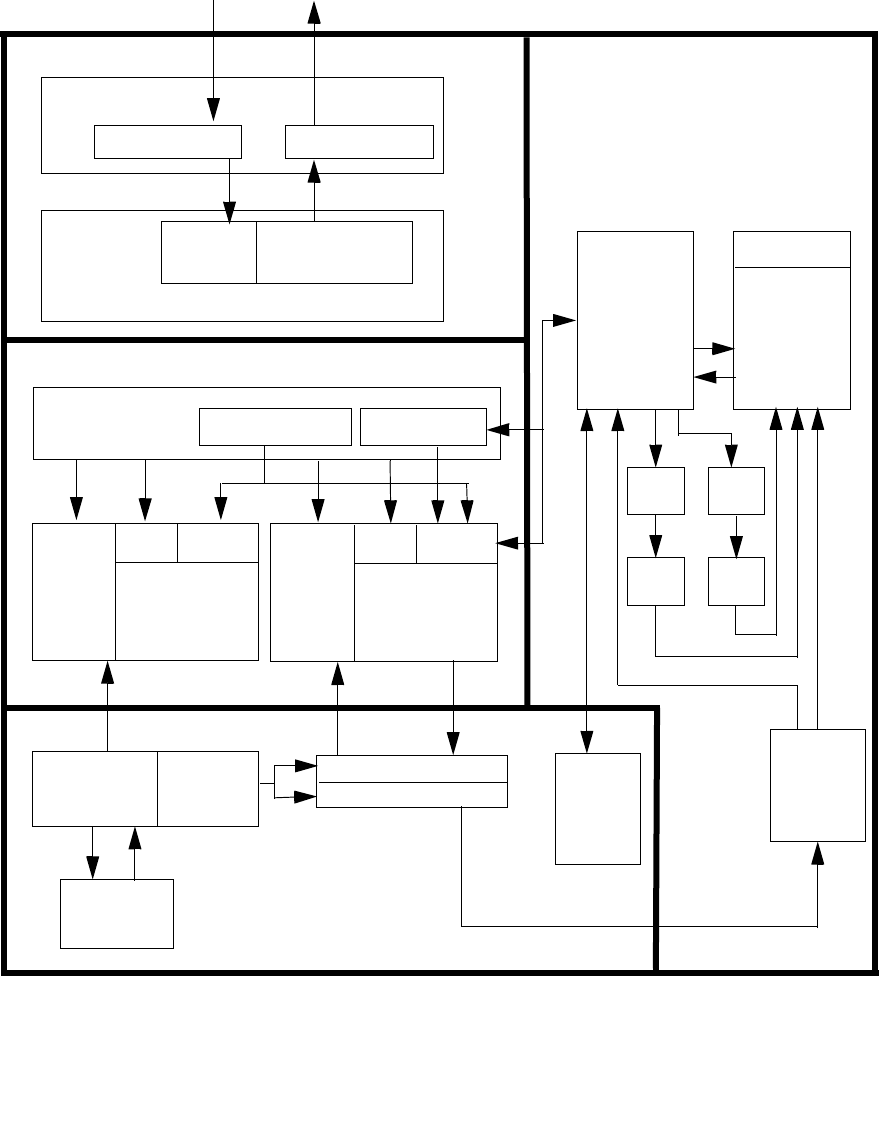

FIGURE 1-1

SPARC64 V Major Units

Extended UPA Bus

UPA interface logic

MoveIn buffer

MoveOut buffer

SX-Unit

U2$ U2$ data

S-Unit interface

tag 2M 4-way

ALUs

FLA

EXA

EXB

FLB

EAGA

EAGB

ALU

Output

Input

Registers

Registers

SX order queue Store queue

SX interface

D-TLB tag data

2048

+ 32

entry

Level-1 D cache

128 KB, 2-way

S-Unit

and

Instruction Instruction

Commit stack entry

Reservation stations

Branch

history

PC

nPC

CCR

FSR

I-Unit

GUB FUB

GPR FPR

E-unit

control

logic

pipeline

fetch buffer

E-Unit

I-TLB tag data

2048

+ 32

entry

Level-1 I cache

128 KB, 2-way