Release 1.0, 1 July 2002 F. Chapter N Interrupt Handling 135

N.2 Interrupt Receive

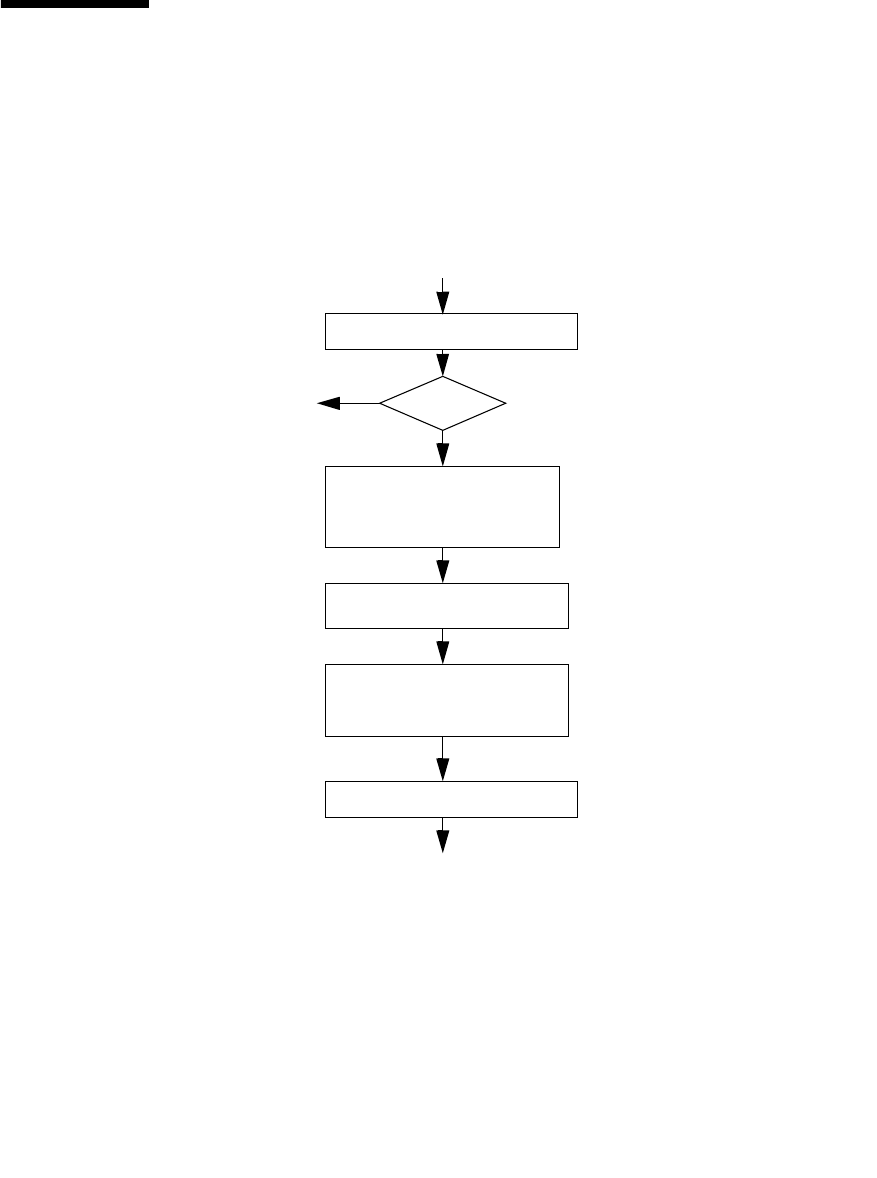

When an interrupt packet is received, eight interrupt data registers are updated with

the associated incoming data and the BUSY bit in the ASI_INTR_RECEIVE register is

set. If interrupts are enabled (PSTATE.IE = 1), then the processor takes a trap and

the interrupt data registers are read by the software to determine the appropriate

trap handler. The handler may reprioritize this interrupt packet to a lower priority.

FIGURE N-2

is an example of the interrupt receive flow.

read ASI_INTR_RECEIVE

Error

Read ASI_INTR_R (data 0)

. . .

Read ASI_INTR_R (data 7)

Determine Trap Handler

Busy?

Y

N

clear ASI_INTR_RECEIVE

interrupt complete

Handle Interrupt or

reprioritize via SOFTINT

FIGURE N-2

Interrupt Receive Flow