7 - 19

7.6.3 List of I/O signals and buffer memory assignment

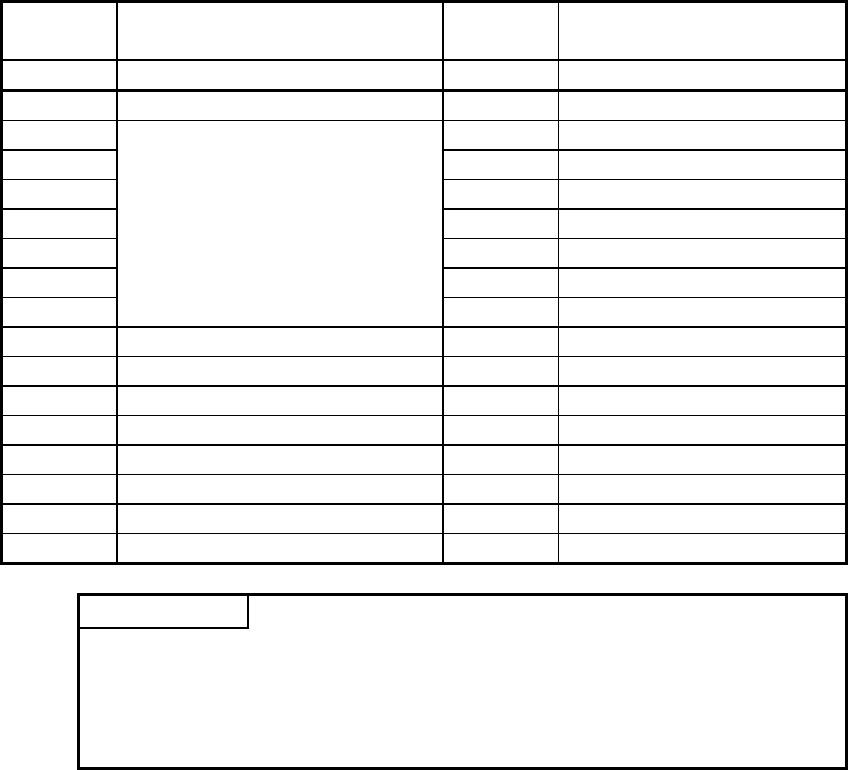

(1) List of I/O signals

The following shows a list of the I/O signals for the D/A converter modules.

The following explanation is mentioned based on the Q68DAVN, Q68DAIN,

Q68DAV and Q68DAI with 8-channel analog output (CH1 to CH8).

Note that I/O numbers (X/Y) shown in this section and thereafter are the values

when the start I/O number for the D/A converter module is set to 0.

Signal

direction

D/A converter module → CPU module

Signal

direction

CPU module

→ D/A converter module

Device No. Signal name Device No. Signal name

X0 Module READY Y0 Use prohibited

*1

X1 Y1 CH1 Output enable/disable flag

X2 Y2 CH2 Output enable/disable flag

X3 Y3

*2

CH3 Output enable/disable flag

X4 Y4

*2

CH4 Output enable/disable flag

X5 Y5

*2

CH5 Output enable/disable flag

X6 Y6

*2

CH6 Output enable/disable flag

X7

Use prohibited

*1

Y7

*2

CH7 Output enable/disable flag

X8 High resolution mode status flag Y8

*2

CH8 Output enable/disable flag

X9 Operating condition setting completed flag Y9 Operating condition setting request

XA Offset/gain setting mode flag YA User range writing request

XB Channel change completed flag YB Channel change request

XC Set value change completed flag YC Set value change request

XD Synchronous output mode flag YD Synchronous output request

XE Use prohibited

*1

YE Use prohibited

*1

XF Error flag YF Error clear request

POINT

*1: These signals cannot be used by the user since they are for system use only.

If these are turned on/off by the sequence program, the functioning of the D/A

converter module cannot be guaranteed.

*2: For the Q62DAN and Q62DA, the use of Y3 to Y8 is prohibited.

For the Q64DAN and Q64DA, the use of Y5 to Y8 is prohibited.