System Control Coprocessor

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 4-20

ID013010 Non-Confidential, Unrestricted Access

To access the Processor Feature Register 1 read CP15 with:

MRC p15, 0, <Rd>, c0, c1, 1 ; Read Processor Feature Register 1

4.2.8 c0, Debug Feature Register 0

The Debug Feature Register 0 provides information about the debug system for the processor.

Debug Feature Register 0 is:

• a read-only register

• accessible in Privileged mode only.

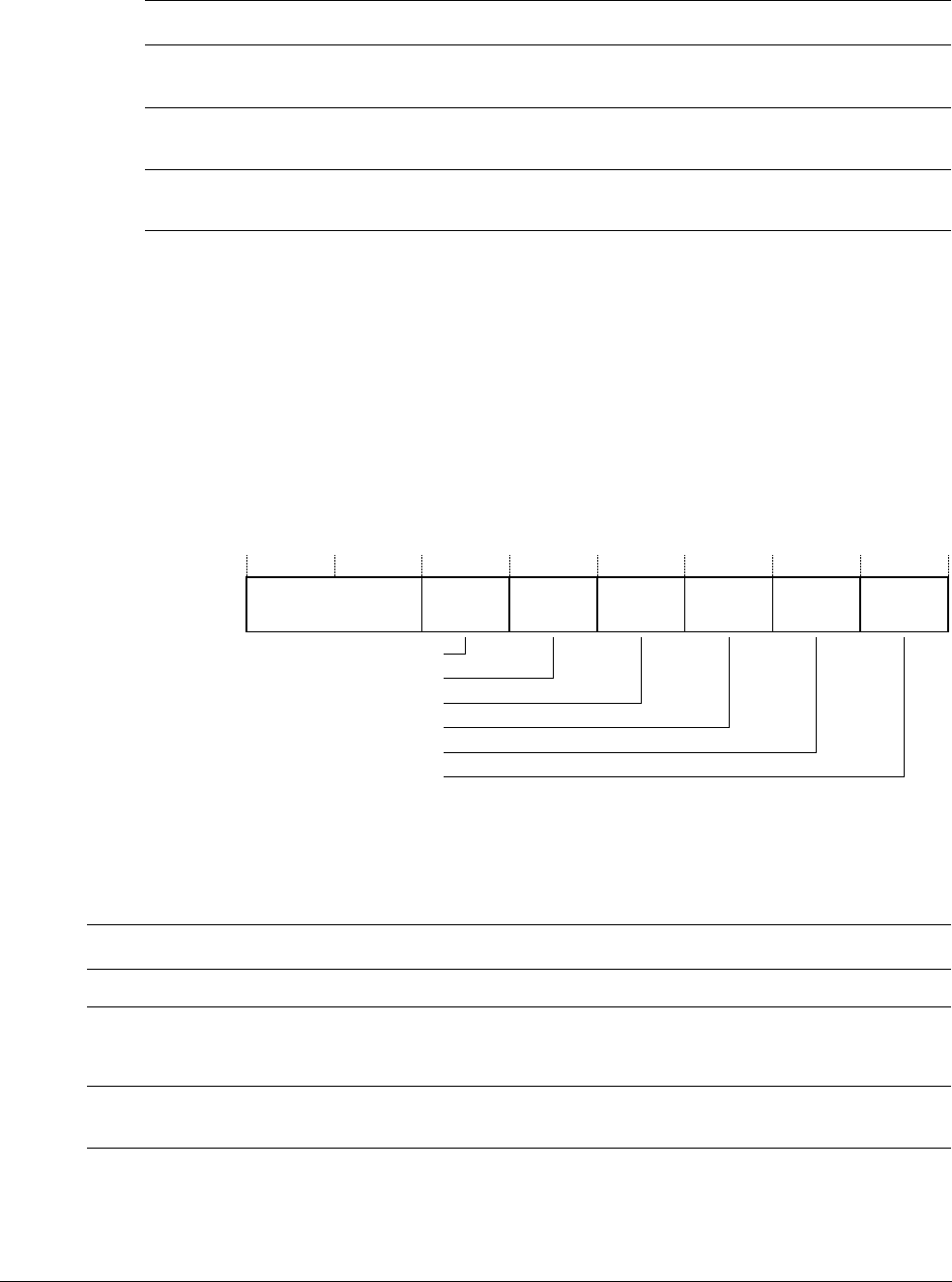

Figure 4-14 shows the bit arrangement for Debug Feature Register 0.

Figure 4-14 Debug Feature Register 0 format

Table 4-9 shows how the bit values correspond with the Debug Feature Register 0 functions.

[11:8] Microcontroller programmer’s model Indicates support for Microcontroller programmer’s model:

0x0

, no support.

[7:4] Security extension Indicates support for Security Extensions Architecture:

0x0

, no support.

[3:0] ARMv4 Programmer’s model Indicates support for standard ARMv4 programmer’s model:

0x1

, the processor supports the ARMv4 model.

Table 4-8 Processor Feature Register 1 bit functions (continued)

Bits Field Function

Reserved

Microcontroller debug model – memory mapped

Trace debug model – memory mapped

Trace debug model – coprocessor

Core debug model – memory mapped

Core debug model – coprocessor

Secure debug model

31 24 23 20 19 16 15 12 11 8 7 4 3 0

Table 4-9 Debug Feature Register 0 bit functions

Bits Field Function

[31:24] Reserved SBZ.

[23:20] Microcontroller

Debug model -

memory mapped

Indicates support for the microcontroller debug model - memory mapped:

0x0

, no support.

[19:16] Trace debug model -

memory mapped

Indicates support for the trace debug model - memory mapped:

0x1

, trace supported, memory mapped access.

[15:12] Trace debug model -

coprocessor

Indicates support for the trace debug model - coprocessor:

0x0

, no support.