System Control Coprocessor

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 4-60

ID013010 Non-Confidential, Unrestricted Access

The Slave Port Control Register is:

• a read/write register

• accessible in User and Privileged mode.

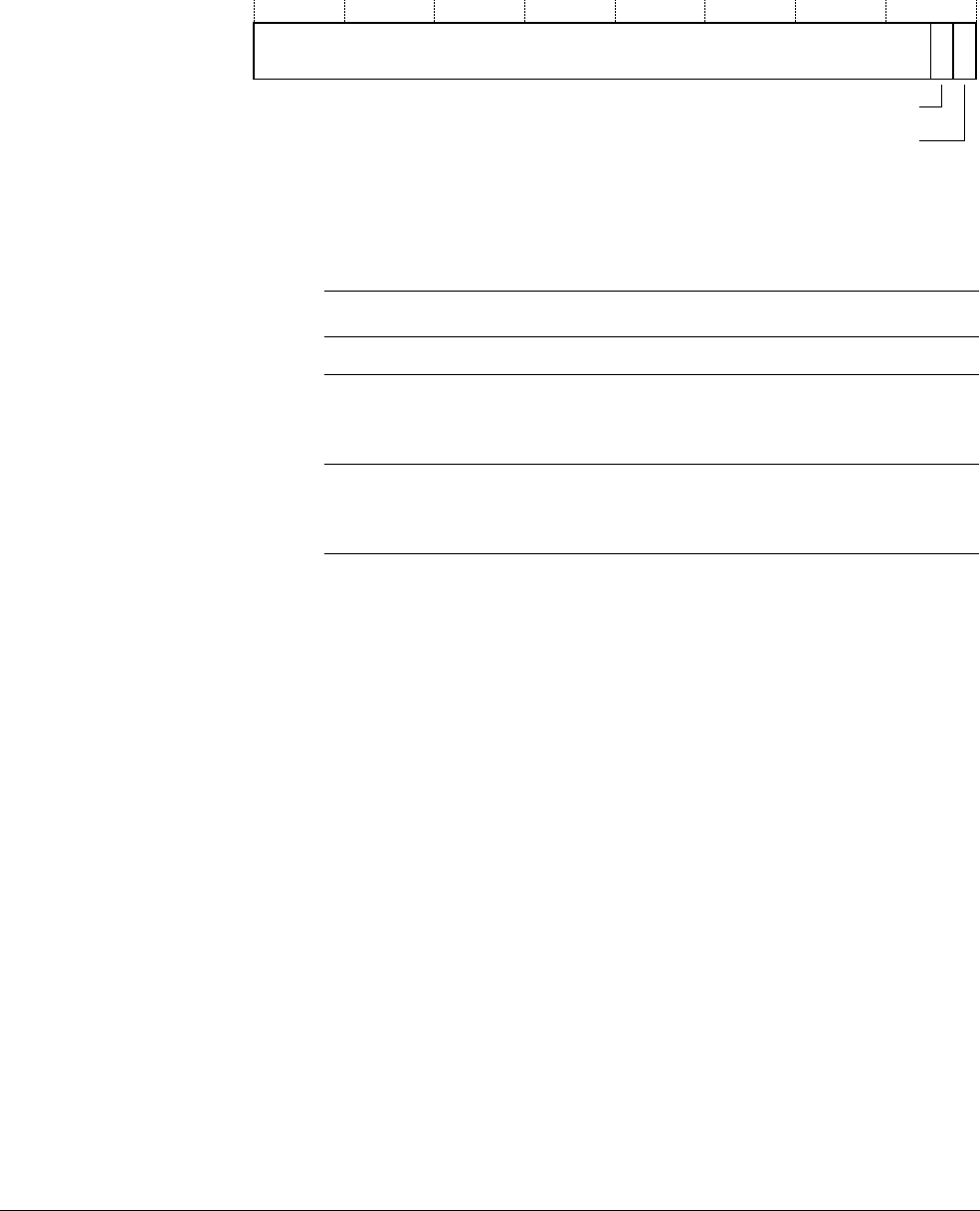

Figure 4-43 shows the arrangement of bits in the register.

Figure 4-43 Slave Port Control Register

Table 4-41 shows how the bit values correspond with the Slave Port Control Register functions.

To access the Slave Port Control Register, read or write CP15 with:

MRC p15, 0, <Rd>, c11, c0, 0 ; Read Slave Port Control Register

MCR p15, 0, <Rd>, c11, c0, 0 ; Write Slave Port Control Register

4.2.25 c13, FCSE PID Register

This processor does not support Fast Context Switch Extension (FCSE).

The FCSE Process IDentifier (PID) Register is accessible in Privileged mode only. This register

reads as zero and ignores writes.

4.2.26 c13, Context ID Register

The Context ID Register holds a process IDentification (ID) value for the currently-running

process.

The Embedded Trace Macrocell (ETM) and the debug logic use this register. The ETM can

broadcast its value to indicate the process that is running currently. You must program each

process with a unique number.

The Context ID value can also enable process dependent breakpoints and instructions.

The Context ID Register is:

• a read/write register

• accessible in Privileged mode only.

Reserved

31 210

Privilege access

AXI slave enable

Table 4-41 Slave Port Control Register bit functions

Bits Field Function

[31:2] Reserved RAZ/UNP

[1] Privilege access Defines level of access for TCM accesses:

0 = Non-privileged and privileged access, reset value

1 = Privileged access only.

[0] AXI slave enable Enables or disables the AXI slave port for TCM accesses:

0 = Enables AXI slave port, reset value

1 = Disables AXI slave port.