System Control Coprocessor

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 4-36

ID013010 Non-Confidential, Unrestricted Access

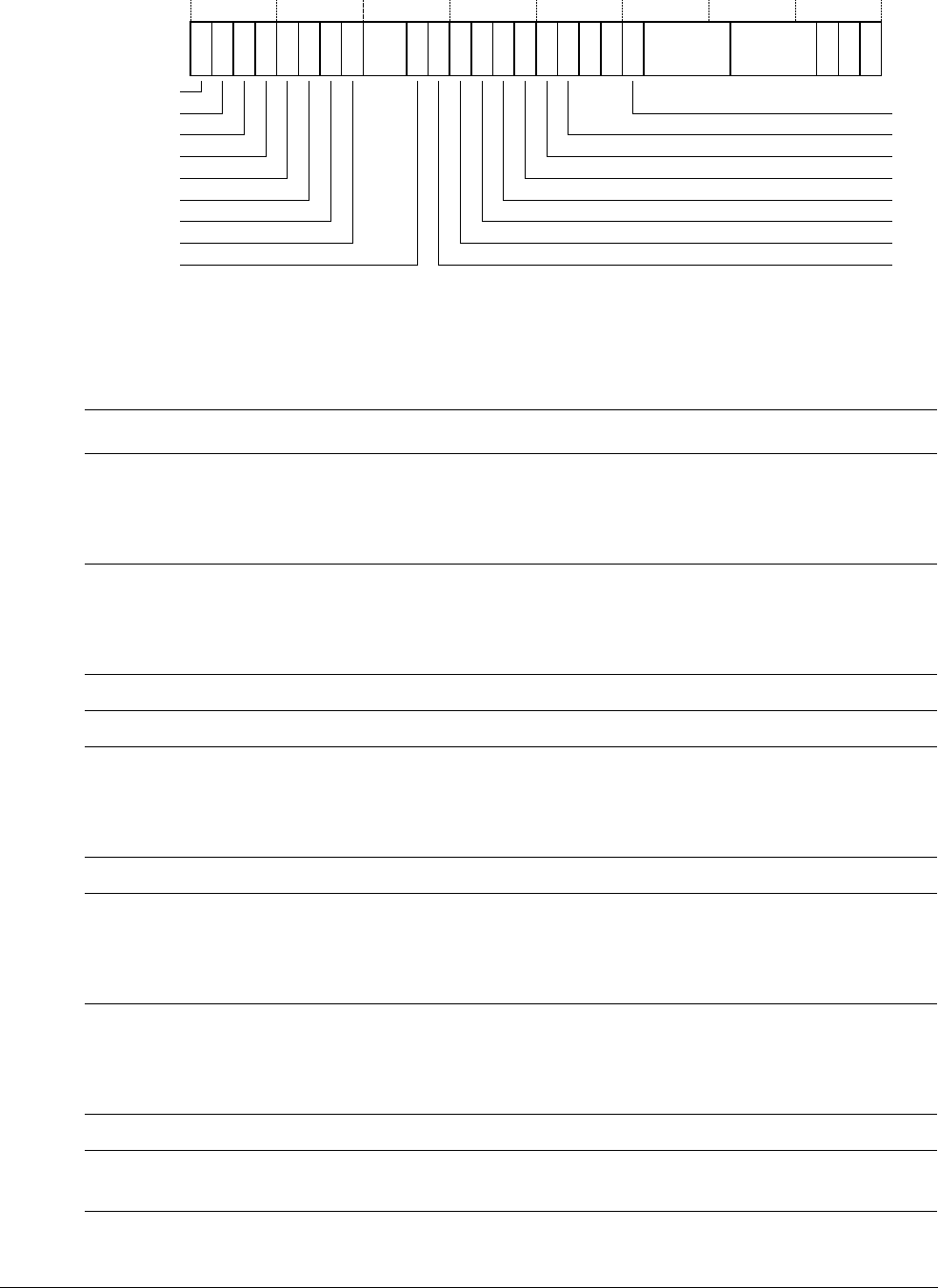

Figure 4-27 System Control Register format

Table 4-23 shows the purposes of the individual bits in the System Control Register.

TRE

IE

TE

AFE

NMFI

SBZ

EE

VE

Z

RR

SBZ

SBO

BR

SBO

FI

DZ

SBZ

M

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 7 6 3 2 1 0

SBO 1 V I SBZ SBO C A

Table 4-23 System Control Register bit functions

Bits Field Function

[31] IE Identifies little or big instruction endianness in use:

0 = little-endianness

1 = big-endianness.

The primary input CFGIE defines the reset value. This bit is read-only.

[30] TE Thumb exception enable:

0 = enable ARM exception generation

1 = enable Thumb exception generation.

The primary input TEINIT defines the reset value.

[29] AFE Access Flag Enable. On the processor this bit is SBZ.

[28] TRE TEX Remap Enable. On the processor this bit is SBZ.

[27] NMFI NMFI, non-maskable fast interrupt enable:

0 = Software can disable FIQs

1 = Software cannot disable FIQs.

This bit is read-only. The configuration input CFGNMFI defines its value.

[26] Reserved SBZ.

[25] EE Determines how the E bit in the CPSR is set on an exception:

0 = CPSR E bit is set to 0 on an exception

1 = CPSR E bit is set to 1 on an exception.

The primary input CFGEE defines the reset value.

[24] VE Configures vectored interrupt:

0 = offset for IRQ = 0x18

1 = VIC controller provides offset for IRQ.

The reset value of this bit is 0.

[23:22] Reserved SBO.

[21] FI Fast Interrupts enable.

On the processor Fast Interrupts are always enabled. This bit is SBO.

[20] Reserved SBZ.