AC Characteristics

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 15-3

ID013010 Non-Confidential, Unrestricted Access

15.2 Processor timing parameters

This section describes the input and output port timing parameters for the processor.

The maximum timing parameter or constraint delay for each processor signal applied to the SoC

is given as a percentage in Table 15-1 to Table 15-17 on page 15-11. The input and output delay

columns provide the maximum and minimum time as a percentage of the processor clock cycle

given to the SoC for that signal.

This section describes:

• Input port timing parameters

• Output ports timing parameters on page 15-8.

15.2.1 Input port timing parameters

Table 15-1 shows the timing parameters for the miscellaneous input ports.

Table 15-2 shows the timing parameters for the configuration input port.

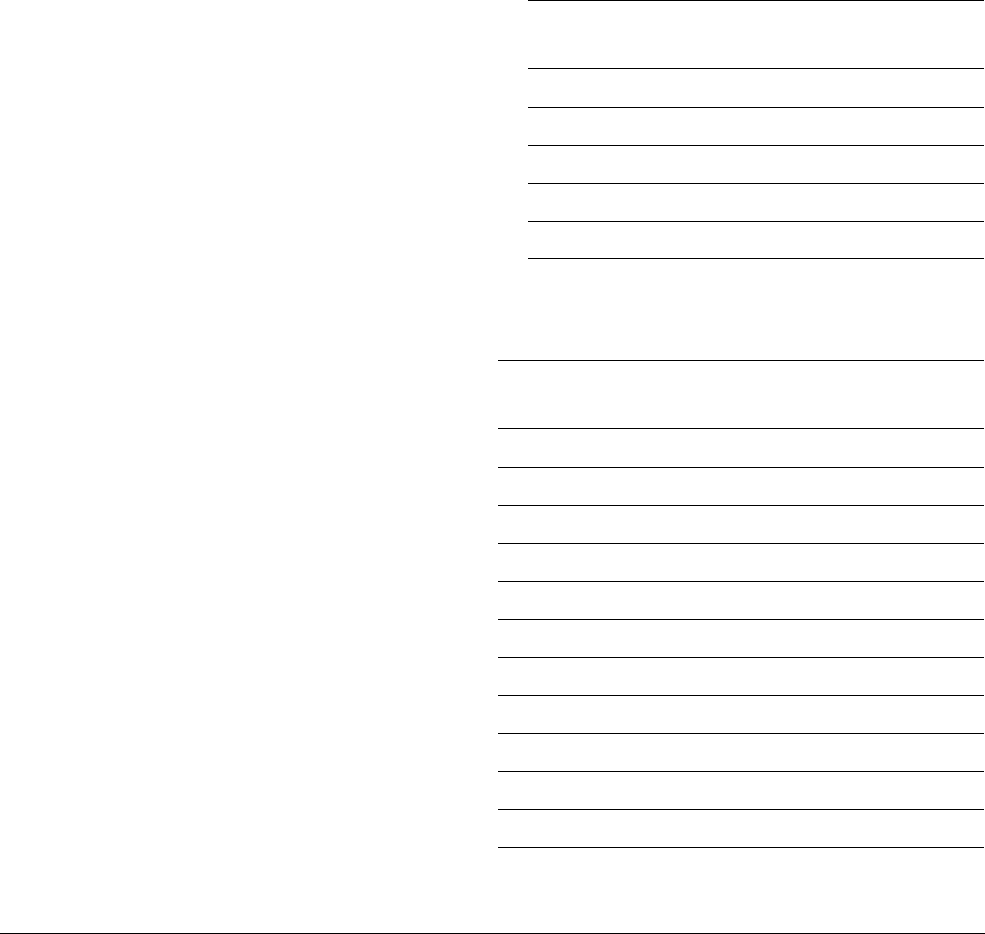

Table 15-1 Miscellaneous input ports timing parameters:

Input delay

minimum

Input delay

maximum

Signal name

Clock uncertainty 10% nRESET

Clock uncertainty 10% nSYSPORESET

Clock uncertainty 10% PRESETDBGn

Clock uncertainty 50% nCPUHALT

Clock uncertainty 20% DBGNOCLKSTOP

Table 15-2 Configuration input port timing parameters

Input delay

minimum

Input delay

maximum

Signal name

Clock uncertainty 20% VINITHI

Clock uncertainty 20% CFGEE

Clock uncertainty 20% CFGIE

Clock uncertainty 20% INITRAMA

Clock uncertainty 20% INITRAMB

Clock uncertainty 20% LOCZRAMA

Clock uncertainty 20% TEINIT

Clock uncertainty 20% CFGNMFI

Clock uncertainty 20% CFGATCMSZ[3:0]

Clock uncertainty 20% CFGBTCMSZ[3:0]

Clock uncertainty 20% PARECCENRAM[2:0]

Clock uncertainty 20% ERRENRAM[2:0]