System Control Coprocessor

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 4-50

ID013010 Non-Confidential, Unrestricted Access

CP15, c9 sets the location of the TCM base address. For more information see c9, BTCM

Region Register on page 4-57 and c9, ATCM Region Register on page 4-58.

c6, MPU Region Base Address Registers

The MPU Region Base Address Registers describe the base address of the region specified by

the Memory Region Number Register. The region base address must always align to the region

size.

The MPU Region Base Address Registers are:

• 32-bit read/write registers

• accessible in Privileged mode only.

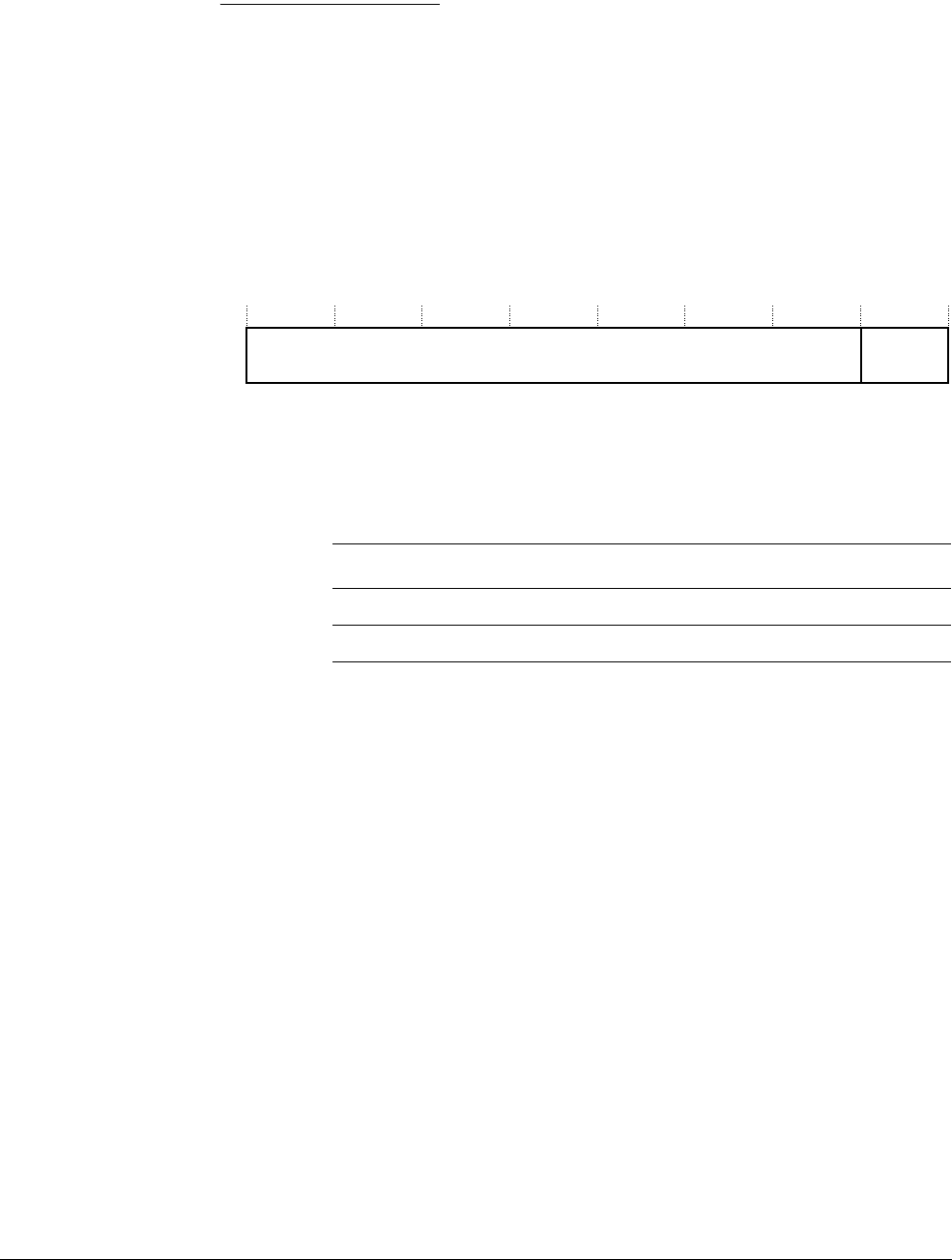

Figure 4-34 shows the arrangement of bits in the registers.

Figure 4-34 MPU Region Base Address Registers format

Table 4-31 shows how the bit values correspond with the MPU Region Base Address Register

functions.

To access an MPU Region Base Address Register, read or write CP15 with:

MRC p15, 0, <Rd>, c6, c1, 0 ; Read MPU Region Base Address Register

MCR p15, 0, <Rd>, c6, c1, 0 ; Write MPU Region Base Address Register

c6, MPU Region Size and Enable Registers

The MPU Region Size and Enable Registers:

• specify the size of the region specified by the Memory Region Number Register

• identify the address ranges that are used for a particular region

• enable or disable the region, and its sub-regions, specified by the Memory Region

Number Register.

The MPU Region Size and Enable Registers are:

• 32-bit read/write registers

• accessible in Privileged mode only.

Figure 4-35 on page 4-51 shows the arrangement of bits in the registers.

31 0

Base address

45

Reserved

Table 4-31 MPU Region Base Address Registers bit functions

Bits Field Function

[31:5] Base address Physical base address. Defines the base address of a region.

[4:0] Reserved SBZ