System Control Coprocessor

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 4-55

ID013010 Non-Confidential, Unrestricted Access

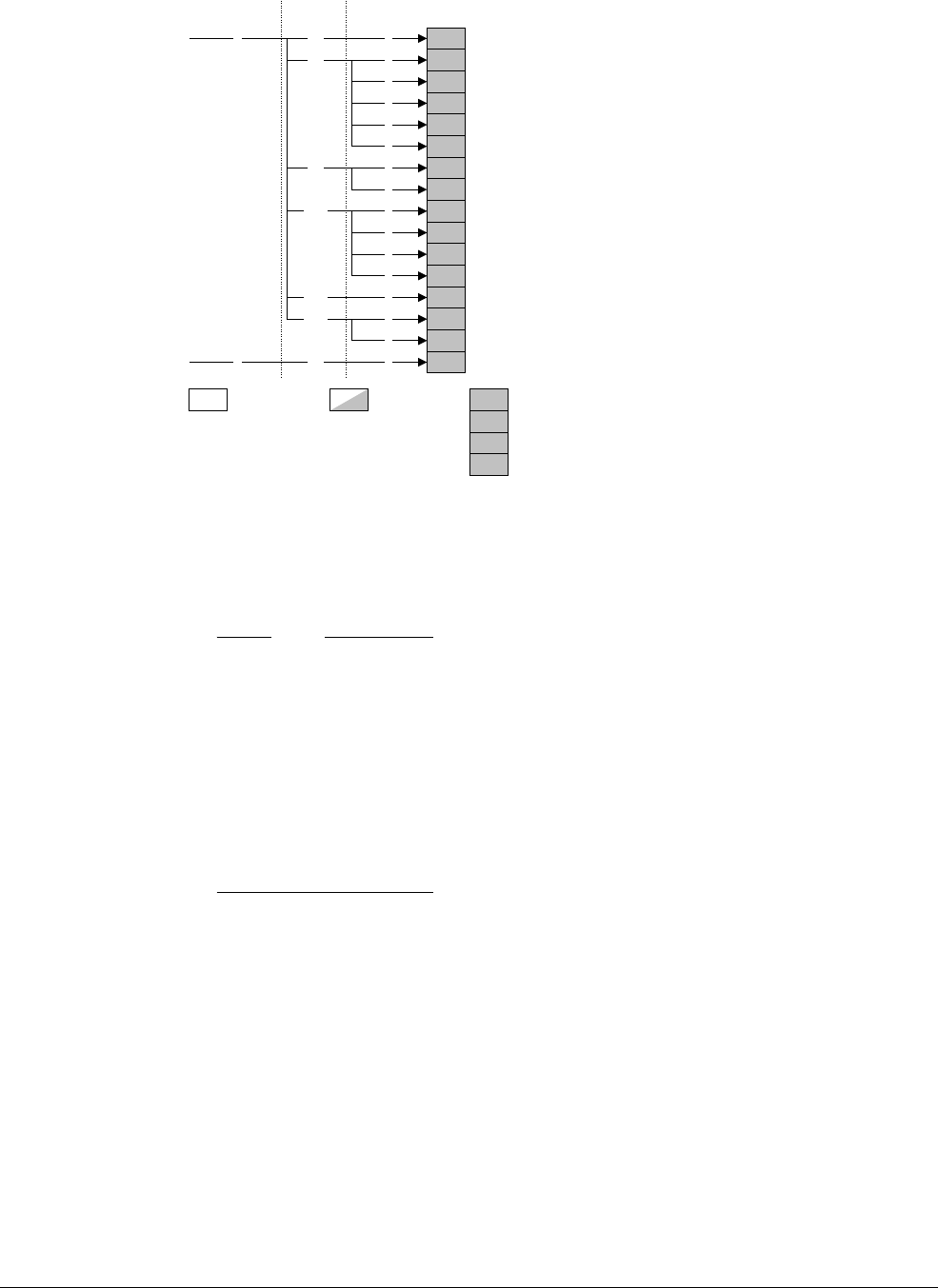

Figure 4-38 Cache operations

In addition to the register c7 cache management functions in this processor, an Invalidate all

data caches operation is provided as a c15 operation. For convenience, that c15 operation is also

described in this section.

Note

• Writing c7 with a combination of CRm and Opcode_2 not listed in Figure 4-38 results in

an Undefined exception.

• In this processor, reading from c7 causes an Undefined exception.

• All accesses to c7 can only be executed in a Privileged mode of operation, except for the

Flush Prefetch Buffer, Data Synchronization Barrier, and Data Memory Barrier

operations. These can be performed in User mode. Attempting to execute a Privileged

instruction in User mode results in an Undefined exception.

• This processor does not contain an address-based branch predictor array.

Invalidate and clean operations

The terms that describe the invalidate, clean, and prefetch operations are defined in the ARM

Architecture Reference Manual.

You can perform invalidate and clean operations on:

• single cache lines

• entire caches.

Set and Way format

Figure 4-39 on page 4-56 shows the Set and Way format for invalidate and clean operations.

c7

SBZ

SBZ

MVA

SBZ

MVA

Way

MVA

Way

SBZ

SBZ

MVA

Way

Invalidate data cache line by set/way

Invalidate data cache line to Point-of-Coherency by MVA

Invalidate entire branch predictor array (NOP)

Wait For Interrupt (NOP)

Flush Prefetch buffer

Invalidate VA from Branch Predictor Array (NOP)

Invalidate All Instruction Caches

Invalidate Instruction Cache Line to Point-of-Unification by MVA

Clean data cache line to Point-of-Unification by MVA

Clean data cache line to Point-of-Coherency by MVA

Clean data cache line by set/way

Data Synchronization Barrier

Data Memory Barrier

Clean and Invalidate data cache line to Point-of-Unification by MVA

Clean and Invalidate data cache line by set/way

Opcode_2CRmCRn Opcode_1

SBZ

MVA

SBZ

Should Be Zero

MVA

Way

Using MVA

Using Set and Way

SBZ

Invalidate all Data Caches0c15

Write-only Accessible in User modeRead-only Read/write

4

c0

0

1

4

6

7

c5

1

2

c6

1

c10

2

4

5

1

c11

0

1

c14

2

c50