System Control Coprocessor

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 4-71

ID013010 Non-Confidential, Unrestricted Access

Table 4-52 shows how the bit values correspond to the CFLR when it indicates a correctable

cache error.

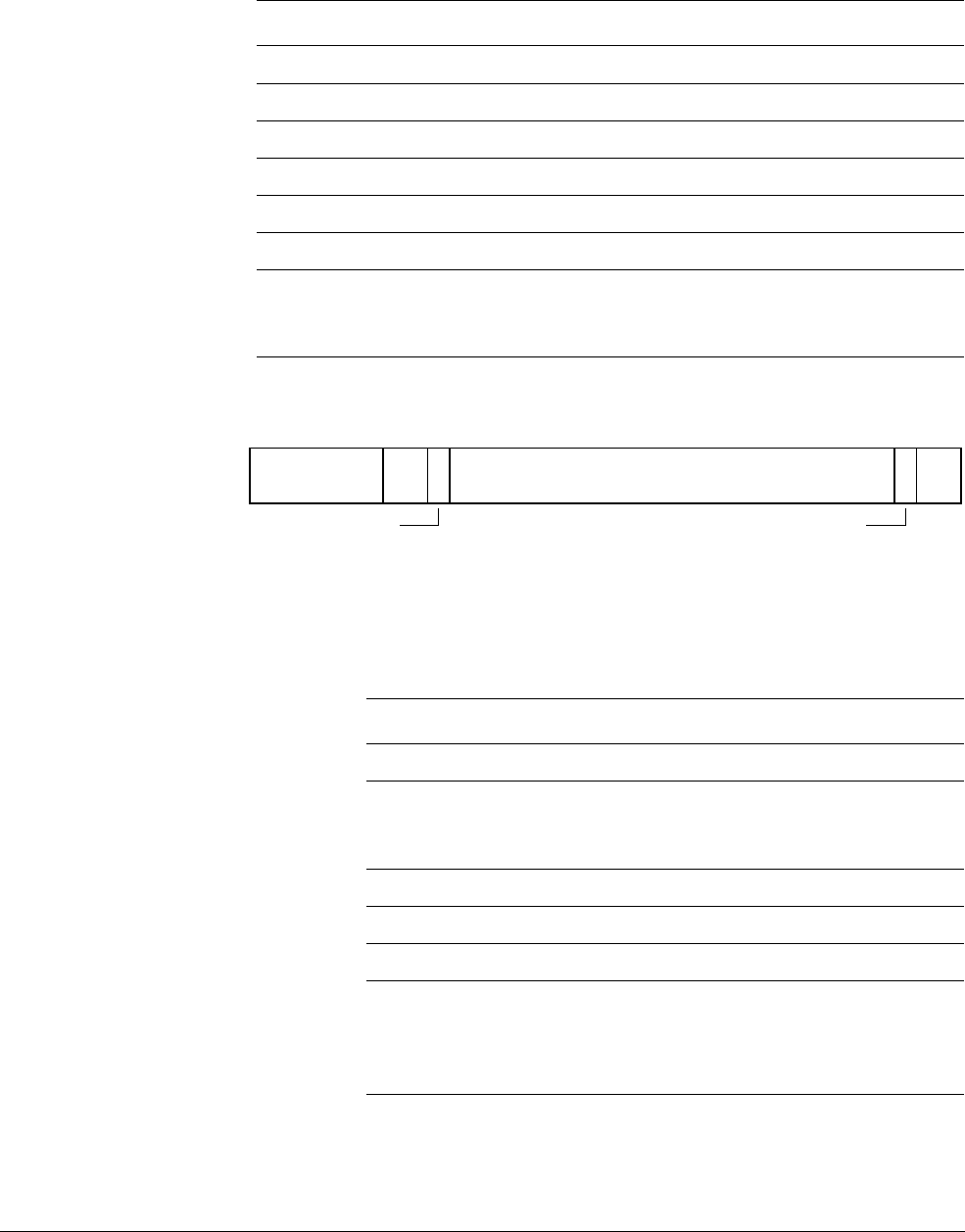

Figure 4-54 shows the bit arrangement of the CFLR when it indicates a correctable TCM error.

Figure 4-54 Correctable Fault Location Register - TCM

Table 4-53 shows how the bit values correspond to the CFLR when it indicates a correctable

TCM error.

To access the Correctable Fault Location Register, read or write CP15 with:

MRC p15, 0, <Rd>, c15, c3, 0 : Read CFLR

MCR p15, 0, <Rd>, c15, c3, 0 : Write CFLR

Table 4-52 Correctable Fault Location Register - cache

Bits Field Function

[31:30] Reserved RAZ

[29:26] Way Indicates the Way of the error.

[25:24] Side Indicates the source of the error. For cache errors, this value is always

0b00

.

[23:14] Reserved RAZ

[13:5] Index Indicates the index of the location where the error occurred.

[4:2] Reserved RAZ

[1:0] Type Indicates the type of access that caused the error.

0b00

= Instruction cache.

0b01

= Data cache.

Type

31 26 25 24 23

22

3210

Reserved Side

Address[22:3]

Reserved Reserved

Table 4-53 Correctable Fault Location Register - TCM

Bits Field Function

[31:26] Reserved RAZ

[25:24] Side Indicates the source of the error.

0b01

= ATCM

0b10

= BTCM

[23] Reserved RAZ

[22:3] Address Indicates the address in the TCM where the error occurred.

[2] Reserved RAZ

[1:0] Type Indicates the type of access that caused the error.

0b00

= Instruction.

0b01

= Data.

0b10

,

0b11

= AXI slave.