Introduction

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 1-13

ID013010 Non-Confidential, Unrestricted Access

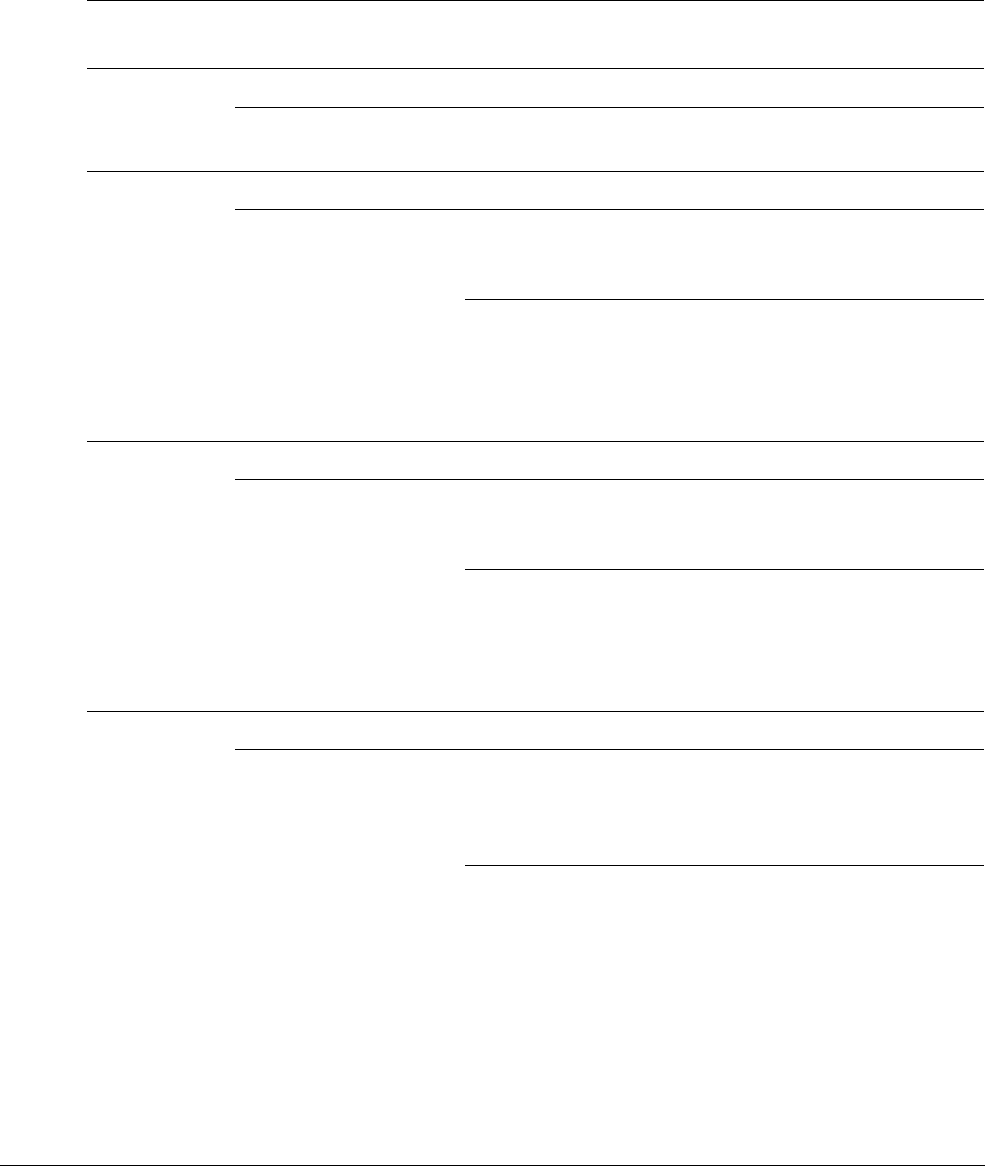

1.6 Configurable options

Table 1-1 shows the features of the processor that can be configured using either

build-configuration or pin-configuration. See Product documentation, design flow, and

architecture on page 1-21 for information about configuration of the processor. Many of these

features, if included, can also be enabled and disabled during software configuration.

Table 1-1 Configurable options

Feature Options Sub-options

Build-configuration

or pin-configuration

Redundant core Single-core (no redundancy) - Build

Dual-core (redundant) In-phase clocks

Out-of-phase clocks

Build

Instruction cache No i-cache - Build

i-cache included No error checking

Parity error checking

64-bit ECC error checking

Build

4KB (4x1KB ways)

8KB (4x2KB ways)

16KB (4x4KB ways)

32KB (4x8KB ways)

64KB (4x16KB ways)

Build

Data cache No d-cache - Build

d-cache included No error checking

Parity error checking

32-bit ECC error checking

Build

4KB (4x1KB ways)

8KB (4x2KB ways)

16KB (4x4KB ways)

32KB (4x8KB ways)

64KB (4x16KB ways)

Build

ATCM No ATCM ports - Build and pin

One ATCM port No error checking

Parity error checking

32-bit ECC error checking

64-bit ECC error checking

Build

4KB, 8KB, 16KB, 32KB, 64KB,

128KB, 256KB, 512KB, 1MB, 2MB,

4MB, or 8MB

Pin