System Control Coprocessor

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 4-31

ID013010 Non-Confidential, Unrestricted Access

To access the Instruction Set Attributes Register 3 read CP15 with:

MRC p15, 0, <Rd>, c0, c2, 3 ; Read Instruction Set Attributes Register 3

c0, Instruction Set Attributes Register 4, ISAR4

The Instruction Set Attributes Register 4 provides information about the instruction set that the

processor supports beyond the basic set.

The Instruction Set Attributes Register 4 is:

• a read-only register

• accessible in Privileged mode only.

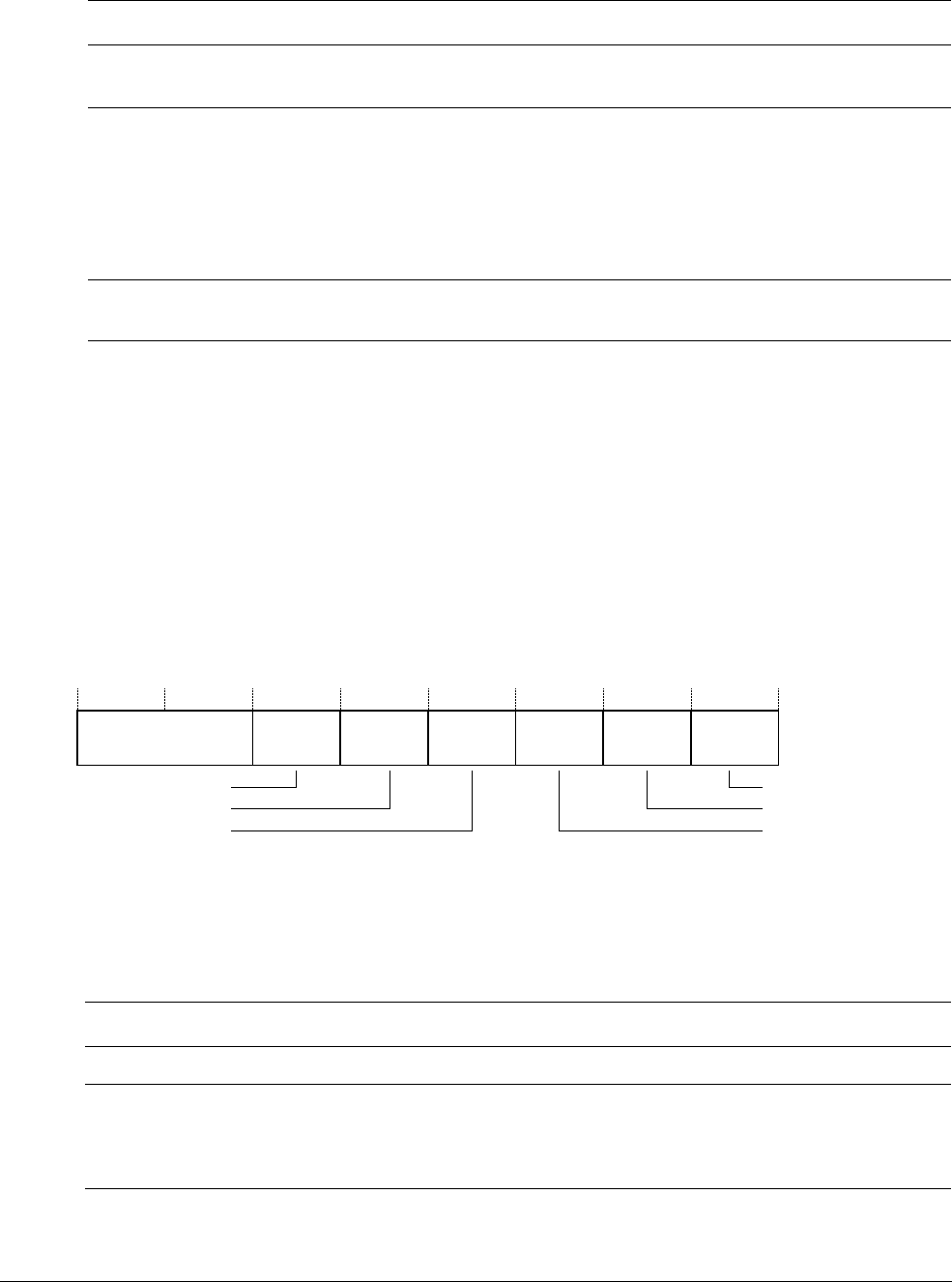

Figure 4-23 shows the bit arrangement for Instruction Set Attributes Register 4.

Figure 4-23 Instruction Set Attributes Register 4 format

Table 4-18 shows how the bit values correspond with the Instruction Set Attributes Register 4

functions.

[11:8] SVC instructions Indicates support for

SVC

(formerly

SWI

) instructions.

0x1

, the processor supports

SVC

.

[7:4] SIMD

instructions

Indicates support for Single Instruction Multiple Data (

SIMD

) instructions.

0x3

, the processor supports:

PKHBT

,

PKHTB

,

QADD16

,

QADD8

,

QASX

,

QSUB16

,

QSUB8

,

QSAX

,

SADD16

,

SADD8

,

SASX

,

SEL

,

SHADD16

,

SHADD8

,

SHASX

,

SHSUB16

,

SHSUB8

,

SHSAX

,

SSAT

,

SSAT16

,

SSUB16

,

SSUB8

,

SSAX

,

SXTAB16

,

SXTB16

,

UADD16

,

UADD8

,

UASX

,

UHADD16

,

UHADD8

,

UASX

,

UHSUB16

,

UHSUB8

,

USAX

,

UQADD16

,

UQADD8

,

UQASX

,

UQSUB16

,

UQSUB8

,

UQSAX

,

USAD8

,

USADA8

,

USAT

,

USAT16

,

USUB16

,

USUB8

,

USAX

,

UXTAB16

,

UXTB16

,

and the GE[3:0] bits in the PSRs.

[3:0] Saturate

instructions

Indicates support for saturate instructions.

0x1

, the processor supports

QADD

,

QDADD

,

QDSUB

,

QSUB

and Q flag in PSRs.

Table 4-17 Instruction Set Attributes Register 3 bit functions (continued)

Bits Field Function

31 24 23 20 19 16 15 12 11 8 7 4 3 0

Exclusive instructions

Barrier instructions

SMC instructions

Write-back instructions

With shift instructions

Unprivileged instructions

Reserved

Table 4-18 Instruction Set Attributes Register 4 bit functions

Bits Field Function

[31:24] Reserved SBZ.

[23:20] Exclusive instructions Indicates support for Exclusive instructions.

0x0

, Only supports synchronization primitive instructions as indicated by bits

[15:12] in the ISAR3 register. See c0, Instruction Set Attributes Register 3, ISAR3

on page 4-30 for more information.

[19:16] Barrier instructions Indicates support for Barrier instructions.

0x1

, the processor supports

DMB

,

DSB

, and

ISB

instructions.