AC Characteristics

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 15-4

ID013010 Non-Confidential, Unrestricted Access

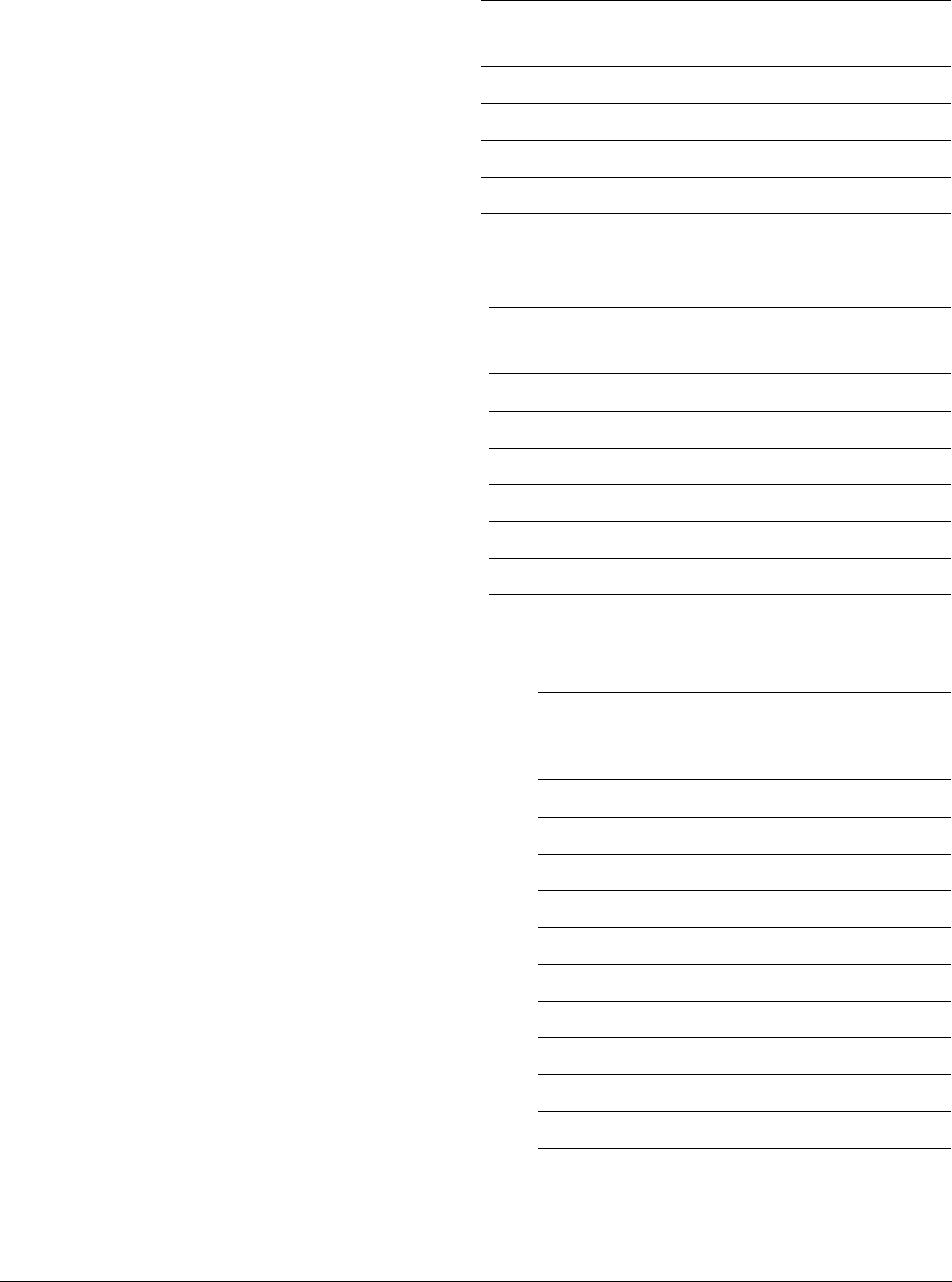

Table 15-3 shows the timing parameters for the interrupt input ports.

Table 15-4 shows the input timing parameters for the AXI master port.

Clock uncertainty 20% PARLVRAM

Clock uncertainty 20% ENTCM1IF

Clock uncertainty 20% SLBTCMSB

Clock uncertainty 20% RMWENRAM[1:0]

Table 15-3 Interrupt input ports timing parameters

Input delay

minimum

Input delay

maximum

Signal name

Clock uncertainty 60% nFIQ

Clock uncertainty 60% nIRQ

Clock uncertainty 10% INTSYNCEN

Clock uncertainty 60% IRQADDRV

Clock uncertainty 60% IRQADDRVSYNCEN

Clock uncertainty 60% IRQADDR[31:2]

Table 15-4 AXI master input port timing parameters

Input delay

minimum

Input

delay

maximum

Signal name

Clock uncertainty 50% ACLKENM

Clock uncertainty 60% AWREADYM

Clock uncertainty 60% WREADYM

Clock uncertainty 60% BIDM[3:0]

Clock uncertainty 60% BRESPM[1:0]

Clock uncertainty 60% BVALIDM

Clock uncertainty 60% ARREADYM

Clock uncertainty 60% RIDM[3:0]

Clock uncertainty 60% RDATAM[63:0]

Clock uncertainty 60% RRESPM[1:0]

Clock uncertainty 60% RLASTM

Table 15-2 Configuration input port timing parameters (continued)

Input delay

minimum

Input delay

maximum

Signal name