Level One Memory System

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 8-35

ID013010 Non-Confidential, Unrestricted Access

8.7 Memory types and L1 memory system behavior

The behavior of the L1 memory system depends on the type attribute of the memory that is being

accessed:

• Only Normal, Non-shared memory can be cached in the RAMs.

• The store buffer can merge any stores to Normal memory. See Store buffer on page 8-18

for more information.

• Only Normal memory is considered restartable, that is, a multi-word transfer can be

abandoned part way through because of an interrupt, to be restarted after the interrupt has

been handled. See Interrupts on page 2-18 for more information about interrupt behavior.

• Only the internal exclusive monitor is used for exclusive accesses to Non-shared memory.

Exclusive accesses to shared memory are checked using the internal monitor and also, if

necessary, any external monitor, using the L2 memory interface.

• Accesses resulting from

SWP

and

SWPB

instructions to Cacheable memory are not marked

as locked when performed using the L2 memory interface.

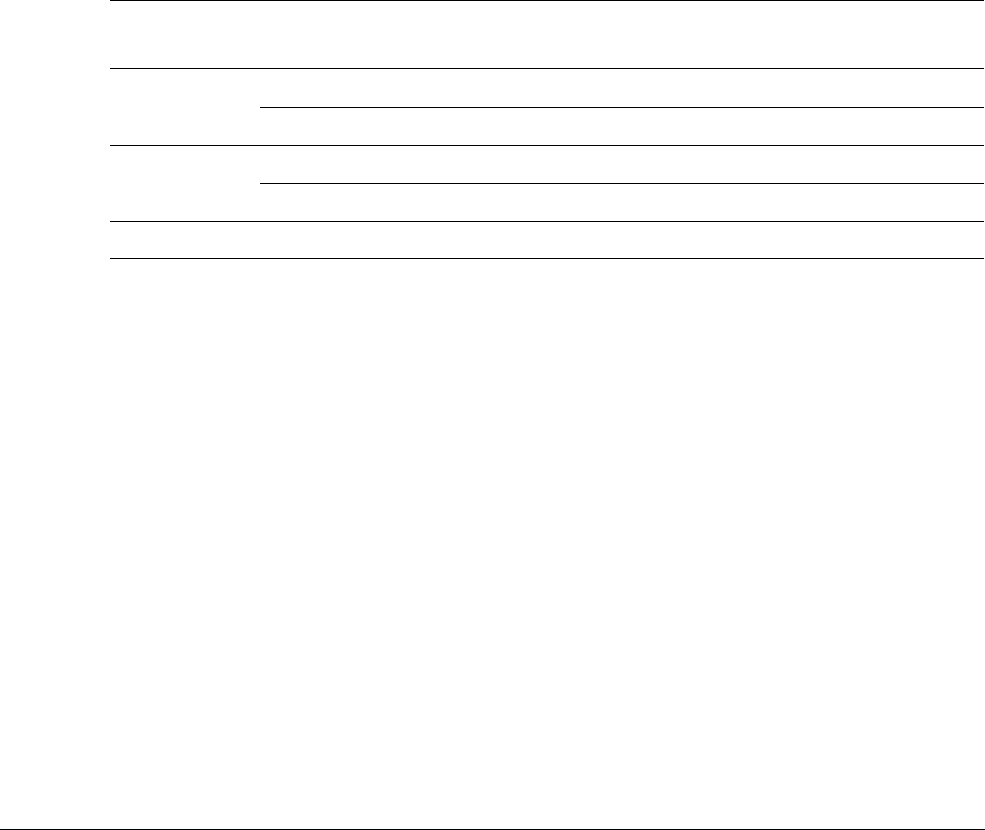

Table 8-17 summarizes the processor memory types and associated behavior.

Table 8-17 Memory types and associated behavior

Memory type Cacheable Merging Restartable

Internal

exclusives

Locked

swaps

Normal Shared No Yes Yes Partially Yes

Non-shared Yes Yes Yes Yes No

Device Shared No No No Partially Yes

Non-shared No No No Yes Yes

Strongly Ordered Shared No No No Partially Yes