System Control Coprocessor

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 4-48

ID013010 Non-Confidential, Unrestricted Access

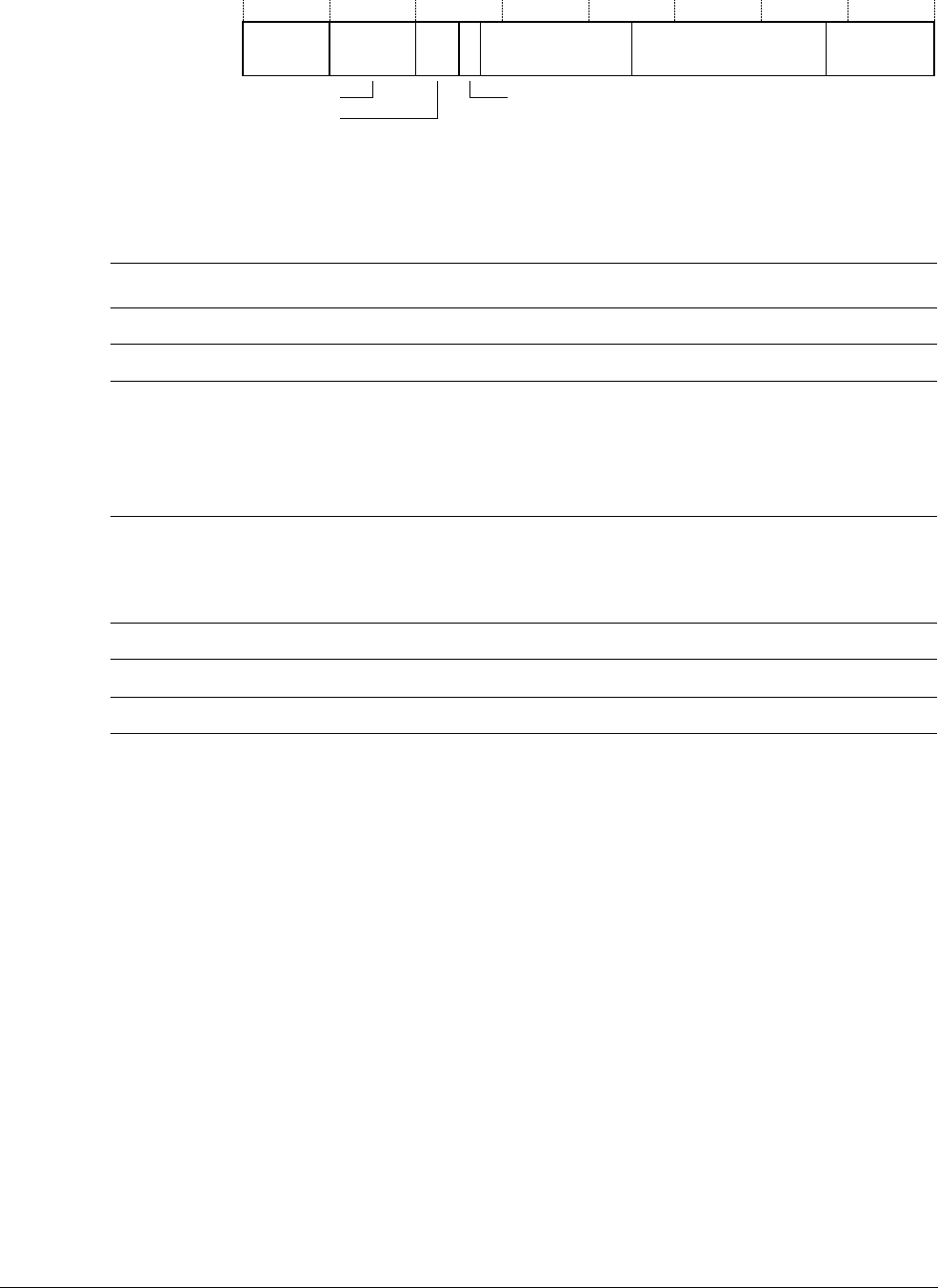

Figure 4-33 Auxiliary fault status registers format

Table 4-30 shows how the bit values correspond with the auxiliary fault status register functions.

To access the auxiliary fault status registers, read or write CP15 with:

MCR p15, 0, <Rd>, c5, c1, 0 ; Write Auxiliary Data Fault Status Register

MRC p15, 0, <Rd>, c5, c1, 0 ; Read Auxiliary Data Fault Status Register

MCR p15, 0, <Rd>, c5, c1, 1 ; Write Auxiliary Instruction Fault Status Register

MRC p15, 0, <Rd>, c5, c1, 1 ; Read Auxiliary Instruction Fault Status Register

The contents of an auxiliary fault status register are only valid when the corresponding Data or

Instruction Fault Status Register indicates that a parity error has occurred. At other times the

contents of the auxiliary fault status registers are Unpredictable.

c6, Data Fault Address Register

The Data Fault Address Register (DFAR) holds the address of the fault when a precise abort

occurs.

The DFAR is:

• a read/write register

• accessible in Privileged mode only.

Reserved IndexReserved

31 0

Reserved

4

27 24 23 22 14 13 5

CacheWay

Side

28

21 20

Recoverable error

Table 4-30 ADFSR and AIFSR bit functions

Bits Field Function

[31:28] Reserved SBZ.

[27:24]

CacheWay

a

The value returned in this field indicates the cache way or ways in which the error occurred.

[23:22] Side The value returned in this field indicates the source of the error. Possible values are:

b00 = Cache or AXI-master interface

b01 = ATCM

b10 = BTCM

b11 = Reserved.

[21] Recoverable

error

The value returned in this field indicates if the error is recoverable.

0 = Unrecoverable error.

1 = Recoverable error. This includes all correctable parity/ECC errors and recoverable

TCM external errors.

[20:14] Reserved SBZ.

[13:5]

Index

b

This field returns the index value for the access giving the error.

[4:0] Reserved SBZ.

a. This field is only valid for data cache store parity/ECC errors, otherwise it is Unpredictable.

b. This field is only valid for data cache store parity/ECC errors. On the AIFSR, and for TCM accesses, this field SBZ.