System Control Coprocessor

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 4-34

ID013010 Non-Confidential, Unrestricted Access

To access the Current Cache Size Identification Register read CP15 with:

MRC p15, 1, <Rd>, c0, c0, 0 ; Read Current Cache Size Identification Register

4.2.13 c0, Current Cache Level ID Register

The Current Cache Level ID Register indicates the cache levels that are implemented.

Architecturally, there can be a different number of cache levels on the instruction and data side.

The register also captures the point-of-coherency and the point-of-unification.

The Current Cache Level ID Register is:

• a read-only register

• accessible in Privileged mode only.

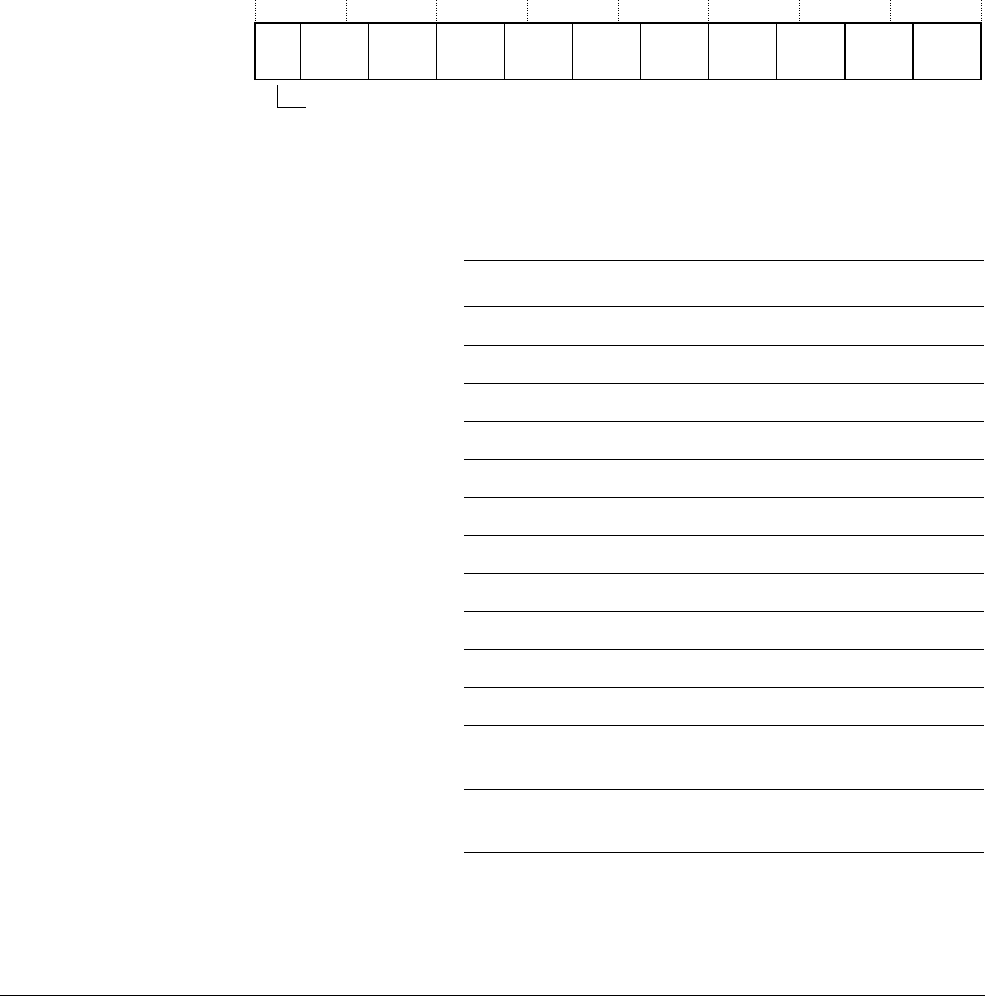

Figure 4-25 shows the bit arrangement for the Current Cache Level ID Register.

Figure 4-25 Current Cache Level ID Register format

Table 4-21 shows how the bit values correspond with the Current Cache Level ID Register.

To access the Current Cache Level ID Register, read CP15 with:

MRC p15, 1, <Rd>, c0, c0, 1 ; Read Current Cache Level ID Register

CL 8 CL 7 CL 6 CL 5 CL 4 CL 3 CL 2 CL 1

Reserved

31 30 29 27 26 24 23 21 20 18 17 15 14 12 11 10 8 6 5 3 2 0

LoU LoC

Table 4-21 Current Cache Level ID Register bit functions

Bits Field Function

[31:30] Reserved SBZ

[29:27] LoU 0b001 = Level of Unification

[26:24] LoC 0b001 = Level of Coherency

[23:21] CL 8 0b000 = no cache at Cache Level (CL) 8

[20:18] CL 7 0b000 = no cache at CL 7

[17:15] CL 6 0b000 = no cache at CL 6

[14:12] CL 5 0b000 = no cache at CL 5

[11:9] CL 4 0b000 = no cache at CL 4

[8:6] CL 3 0b000 = no cache at CL 3

[5:3] CL 2 0b000 = no cache at CL 2

[2] CL 1 RAZ. Indicates no unified cache at CL1

[1] CL 1 0b001 if a data cache is implemented

0b000 if no data cache is implemented

[0] CL 1 0b001 if an instruction cache is implemented

0b000 if no instruction cache is implemented