Debug

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 11-5

ID013010 Non-Confidential, Unrestricted Access

11.3 Debug register interface

You can access the processor debug register map using the APB slave port. This is the only way

to get full access to the processor debug capability. ARM recommends that if your system

requires the processor to access its own debug registers, you choose a system interconnect

structure that enables the processor to access the APB slave port by executing load and stores

to an appropriate area of physical memory.

This section describes:

• Coprocessor registers

• CP14 access permissions

• Coprocessor registers summary

• Memory-mapped registers on page 11-6

• Memory addresses for breakpoints and watchpoints on page 11-7

• Power domains on page 11-8

• Effects of resets on debug registers on page 11-8

• APB port access permissions on page 11-8.

11.3.1 Coprocessor registers

Although most of the processor debug registers are accessible through the memory-mapped

interface, there are several registers that you can access through a coprocessor interface. This is

important for boot-strap access to the register file. It enables software running on the processor

to identify the debug architecture version that the device implements.

11.3.2 CP14 access permissions

By default, you can access all CP14 debug registers from a nonprivileged mode. However, you

can program the processor to disable user-mode access to all coprocessor registers using bit [12]

of the DSCR, see CP14 c1, Debug Status and Control Register on page 11-14 for more

information. CP14 debug registers accesses are always permitted when the processor is in debug

state regardless of the processor mode.

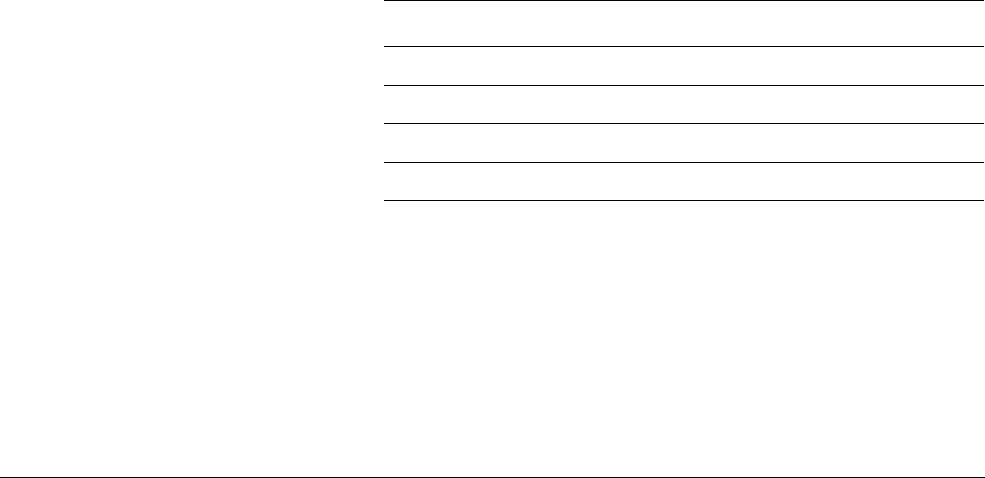

Table 11-1 shows access to the CP14 debug registers.

11.3.3 Coprocessor registers summary

Table 11-2 on page 11-6 shows a set of valid CP14 instructions for accessing the debug

registers. All CP14 instructions not listed are Undefined.

Table 11-1 Access to CP14 debug registers

Debug state Processor mode DSCR[12] CP14 debug access

Yes X X Permitted

No User b0 Permitted

No User b1

Not permitted

a

a. Instructions attempting to access CP14 registers cause the processor to take an

Undefined exception.

No Privileged X Permitted