Debug

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 11-22

ID013010 Non-Confidential, Unrestricted Access

11.4.11 Debug Run Control Register

The DRCR requests the processor to enter or leave debug state. It also clears the sticky

exception bits present in the DSCR.

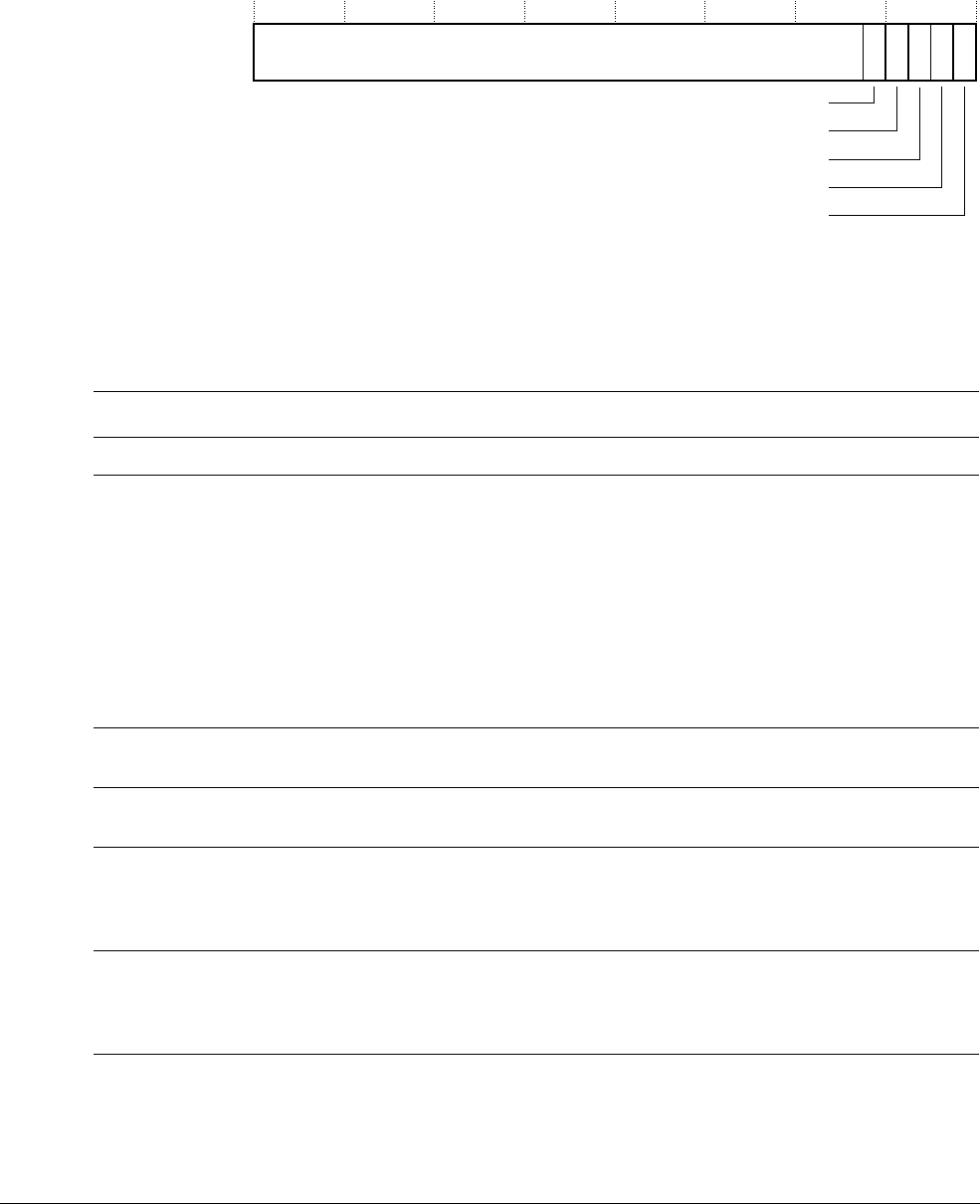

Figure 11-9 shows the bit arrangement of the DRCR.

Figure 11-9 Debug Run Control Register format

Table 11-15 shows how the bit values correspond with the Debug Run Control Register

functions.

31

053

Reserved

Cancel memory request

214

Clear sticky pipeline advance

Clear sticky exceptions

Restart request

Halt request

Table 11-15 Debug Run Control Register functions

Bits Field Function

[31:5] Reserved RAZ.

[4] Cancel memory

requests

If 1 is written to this bit, the processor abandons any pending memory transactions until it

can enter debug state. Debug state entry is the acknowledge event that clears this request.

Abandoned transactions have the following behavior:

• abandoned stores might write an Unpredictable value to the target address

• abandoned loads return an Unpredictable value to the register bank.

An abandoned transaction does not cause any exception. Additional instruction fetches or

data accesses after the processor entered debug state have an Unpredictable behavior.

This bit enables the debugger to progress on a deadlock so the processor can enter debug

state. For a debug state entry to occur, a halting debug event must be requested before this

bit is set. If you write a 1 to this bit when DBGEN is LOW, the write has no effect.

a

[3] Clear sticky

pipeline advance

Writing a 1 to this bit clears DSCR[25].

[2] Clear sticky

exceptions

Writing a 1 to this bit clears DSCR[8:6].

[1] Restart request Writing a 1 to this bit requests that the processor leaves debug state. This request is held

until the processor exits debug state. When the debugger makes this request, it polls

DSCR[1] until it reads 1. This bit always reads as zero. Writes are ignored when the

processor is not in debug state.

[0] Halt request Writing a 1 to this bit triggers a halting debug event, that is, a request that the processor

enters debug state. This request is held until the debug state entry occurs. When the

debugger makes this request, it polls DSCR[0] until it reads 1. This bit always reads as zero.

Writes are ignored when the processor is already in debug state.

a. Entry into debug state is not expected to be recoverable.