Cycle Timings and Interlock Behavior

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 14-35

ID013010 Non-Confidential, Unrestricted Access

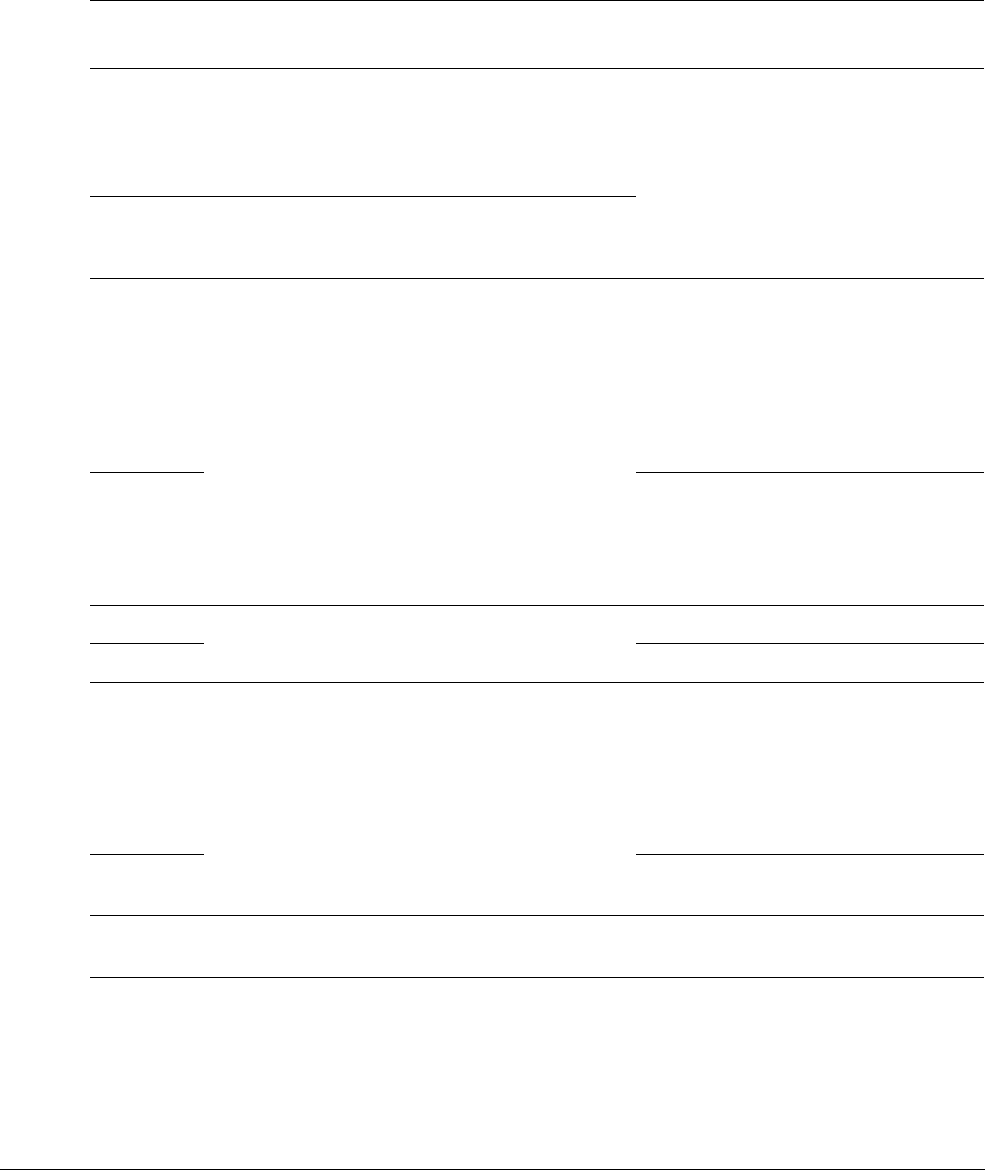

14.23.2 Permitted combinations

Table 14-28 lists the permitted instruction combinations. Any instruction can be conditional or

flag-setting unless otherwise stated. Only the exact instruction combinations listed in

Table 14-28 can be dual issued, provided you ensure the instruction combinations obey the rules

specified in Dual issue rules on page 14-34.

Table 14-28 Permitted instruction combinations

Dual issue

case

First instruction Second instruction

Case A Any instruction other than load/store multiple/double,

flag-setting multiply, non-VFP coprocessor operations,

miscellaneous processor control instructions

a

, or floating

point instructions if floating point logic is not included in

the processor

B #immed

IT

NOP

Case A-F

b

Any floating point instructions, excluding load/store

multiple, double precision

CDP

instructions,

VCVT.F64.F32

,

and

VMRS

and

VMSR

.

Case B1

LDR <Rt>, [<Rn>, #<imm>]

c

LDR <Rt>, [<Rn>, <Rm>]

c

LDR <Rt>, [<Rn>, <Rm>, LSL #1, 2 or 3]

c

Any data processing instruction that does not

require a shift by a register value.

d

Any bitfield, saturate or bit-packing

instruction.

e

Any signed or unsigned extend instruction.

f

Any

SIMD

add or subtract instruction.

g

Other miscellaneous instructions.

h

Case B1-F

b

Any single-precision CDP

i

, excluding

"VMOV.F32 <Sd>, #<imm>"

,

VNEG.F32

,

VABS.F32

,

VCVT.F64.F32

,

VDIV.F32

, and

VSQRT.F32

.

32-bit transfers to and from the floating-point

register file

l

.

Case B2

STR <Rt>, [<Rn>, #<imm>]

c

As for Case B1.

Case B2-F

b

As for Case B1-F

Case C

MOV <Rd>, #immed

jk

MOVW <Rd>, #immed

j

MOV <Rd>, <Rm>

j

Any data processing instruction.

d

Any bitfield, saturate or bit-packing

instruction.

e

Any signed or unsigned extend instruction.

f

Any

SIMD

add or subtract instruction.

g

Other miscellaneous instructions.

h

Case C-F

b

32-bit transfers to and from the floating-point

register file

l

.

Case F1

b

,

m

Any single-precision

CDP

i

, excluding

"VMOV.S32 <Sd>,

#<imm>"

,

VCVT.F64.F32

,

VABS.F32

, and

VNEG.F32

.

As for case C or C-F.

Case F2_ld

b

VLDR.F32

n

As for Case B1 or Case B1-F