Debug

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 11-40

ID013010 Non-Confidential, Unrestricted Access

11.6.2 Halting debug event

The debugger or the system can cause the processor to enter into debug state by triggering any

of the following halting debug events:

• assertion of the EDBGRQ signal, an External Debug Request

• write to the DRCR[0] Halt Request control bit.

If EDBGRQ is asserted while DBGEN is HIGH but invasive debug is not permitted, the

devices asserting this signal must hold it until the processor enters debug state, that is, until

DBGACK is asserted. Otherwise, the behavior of the processor is Unpredictable. For DRCR[0]

halting debug events, the processor records them internally until it is in a state and mode so that

they can be taken.

11.6.3 Behavior of the processor on debug events

This section describes how the processor behaves on debug events while not in debug state. See

Debug state on page 11-44 for information on how the processor behaves while in debug state.

When the processor is in Monitor debug-mode, Prefetch Abort and Data Abort vector catch

debug events are ignored. All other software debug events generate a debug exception such as

Data Abort for watchpoints, and Prefetch Abort for anything else.

When debug is disabled, the

BKPT

instruction generates a debug exception, Prefetch Abort. All

other software debug events are ignored.

When DBGEN is LOW, debug is disabled regardless of the value of DSCR[15:14].

Table 11-39 shows the behavior of the processor on debug events.

11.6.4 Debug event priority

Breakpoint, instruction address or CID match, vector catch, and halting debug events have the

same priority. If more than one of these events occurs on the same instruction, it is

Unpredictable which event is taken.

Breakpoint, instruction address or CID match, vector catch cancel the instruction that they occur

on, therefore a watchpoint cannot be taken on such an instruction.

11.6.5 Watchpoint debug events

A precise watchpoint exception has similar behavior to a precise data abort exception:

• the processor sets R14_abt to the address of the instruction to return to plus

0x08

.

• the processor does not complete the watchpointed instruction.

If the watchpointed access is subject to a precise data abort, then the precise abort takes priority

over the watchpoint because it is a higher priority exception.

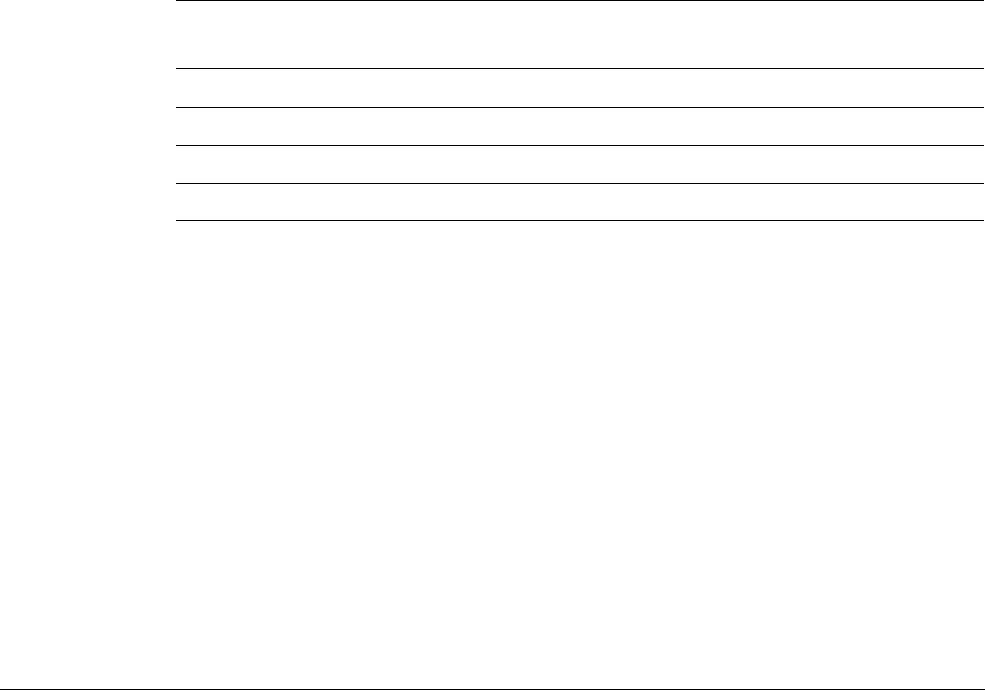

Table 11-39 Processor behavior on debug events

DBGEN DSCR[15:14] Debug mode

Action on software debug

event

Action on halting

debug event

0 bxx Debug disabled Ignore or Prefetch Abort (for

BKPT

) Ignore

1 b00 None Ignore or Prefetch Abort (for

BKPT

) Debug state entry

1 bx1 Halting Debug state entry Debug state entry

1 b10 Monitor Debug exception Debug state entry